3.4【A】CXL,coherence protocol

Intel维护Cache一致性使用的是MESIF协议,在MESI的基础上又增加了一个forward,允许有shared cache line的CPU进行cache和cache之间的数据传输。Cache Line的状态必须是这四个中的一种。CQID : 命令队列ID, 这部分包含与请求相关的跟踪者ID, 当请求的响应和数据返回的时候,其中的 CQID 向设备表明哪一个请求的跟踪索引。:Type 3设

Cache Line的状态必须是这四个中的一种。前三种状态均是数据有效下的状态。Cache Line有两个标志-脏(dirty)和有效(valid)。脏代表该数据和内存不一致。只有干净的数据才能被多个Cache Line共享。

Intel维护Cache一致性使用的是MESIF协议,在MESI的基础上又增加了一个forward,允许有shared cache line的CPU进行cache和cache之间的数据传输。forward指定shared中的一个cache line响应数据请求,cache line有多个shared,但是有一个forward。MESIF主要通过snoop协议完成,但也添加了directory协议的支持,用于调高带宽和效率。

- Core A 读取数据X,缓存行状态为 Exclusive(E)。

- Core B 也读取X,此时Core A的缓存行降为 Shared(S),Core B的缓存行同样为S。

- Core A 修改X,需向总线发送“写请求”(BusRdX),其他核心的X缓存行变为 Invalid(I),Core A的缓存行升为 Modified(M)。

- 当Core B再次读取X时,需从Core A或主存获取最新数据。

将临界区代码标记为“事务”,若执行期间无冲突则原子提交,否则回滚。

RTM(Restricted Transactional Memory):

- 使用

XBEGIN/XEND指令显式定义事务范围。 - 若事务失败(冲突或容量溢出),跳转到

XBEGIN指定的回滚代码路径。

-

HLE(Hardware Lock Elision):

- 通过

XACQUIRE/XRELEASE前缀优化锁操作,尝试无锁执行临界区。 - 若成功,避免锁竞争;失败则退化为传统锁机制。

- 通过

多核之间存在三条线,SHARED负责状态的更新

当要读取a0时

首先应该snop其它核中是否有状态为M或E,

如果有,那么应该让它们先把数据写回到内存当中

然后使其的状态变为S,再

CXL.cache 协议将 Device 和 Host 之间的交互定义为每个具有至少一个关联响应消息的请求的数量,有时是数据传输。 该接口由每个方向的三个通道组成:请求、响应和数据。 通道以其方向命名,D2H 表示Device to Host 和 H2D for Host to Device,以及它们携带的交易、请求、响应和数据

Valid : 说明此请求有效

Opcode : 请求的操作码,表示这个请求的主要功能,重点

Address : 携带的一致性请求的物理地址,因为要对内存进行操作,所以要有对应的地址信息

CQID : 命令队列ID, 这部分包含与请求相关的跟踪者ID, 当请求的响应和数据返回的时候,其中的 CQID 向设备表明哪一个请求的跟踪索引。就是一个唯一标识,用来请求者接收到响应之后,能够区分是响应的哪一个请求

NT :对于可缓存的读,这个区域被作为一个提示,用来向主机表示它应该如何被缓存

-

RspIHit

- 含义:缓存行在 Device 中不存在(Invalid 状态)。

- 用途:表示缓存行未命中,无需进一步操作。

-

RspSHit

- 含义:缓存行在 Device 中处于 Shared(共享) 状态。

- 用途:表示缓存行是干净的,无需写回主存。

-

RspSHitSE

- 含义:缓存行在 Device 中处于 Shared 或 Exclusive(独占) 状态。

- 用途:表示缓存行是干净的,无需写回主存。

-

SnpInvOwn

- 功能:查询 Device 缓存行的状态,使其无效化,并将所有权转移到 Host。

- 用途:用于独占写操作前的缓存行清理和所有权转移。

Hit 后的字母(后缀)

- SE:组合状态,表示缓存行在响应后的状态可以是 Shared 或 Exclusive。具体取决于 Host 的 Snoop 请求类型和后续操作:

- 若 Host 发起

SnpData请求获取数据,Device 返回RspSHitSE后,缓存行仍可能保持 Shared 或 Exclusive。 - 若 Host 发起

SnpInv请求使缓存行无效化,Device 需将状态转为 Invalid,并返回不同的响应(如RspIHitI)。

- 若 Host 发起

| 特性 | RspSHit | RspSHitSE |

|---|---|---|

| 缓存行状态 | 仅 Shared | Shared 或 Exclusive |

| 数据状态 | Clean(与主存一致) | Clean(Shared)或 Clean(Exclusive) |

| 适用 Snoop 请求 | 需要确认缓存行是否为 Shared 状态 | 需要兼容 Shared 和 Exclusive 状态的查询 |

| 典型场景 | Host 需要共享数据且无需写回 | Host 需要获取数据但允许 Device 保留独占权 |

Snoop 交互流程

- Host 发起 Snoop 请求(如 SnpData、SnpInv 等)。

- Device 根据缓存行状态返回对应的 Snoop 响应(如 RspSHitSE、RspSHitM 等)。

- Host 根据响应更新全局一致性状态,并可能触发数据写回或共享。

什么是“所有权”(Ownership)?

在缓存一致性协议中,所有权(Ownership) 表示某个核心或设备对特定缓存行的数据拥有唯一修改权和最新版本。其技术本质是:

- Modified 状态(MESI 中的 M):拥有者持有最新数据,其他缓存中该行的副本均为无效(Invalid)。

- Exclusive 状态(MESI 中的 E):拥有者独占数据,但未修改(与主存一致),可直接写入。

所有权的转移意味着将这种“唯一修改权”从一个实体(如设备)转移到另一个实体(如 Host CPU)。

SnpInvOwn(Snoop Invalidate and Transfer Ownership)是一种缓存一致性指令,常见于异构系统(如 CPU 与 GPU、DMA 设备共享内存)。其功能分两步:

- 使设备的缓存行无效化(Invalidate):强制设备放弃该缓存行的副本。

- 将所有权转移到 Host:确保 Host 获得该缓存行的独占控制权(Exclusive 或 Modified 状态)。

假设一个 DMA 设备正在向内存写入数据,完成后需通知 Host 读取最新数据:

- DMA 设备完成写入,缓存行处于 Modified 状态。

- Host 发起

SnpInvOwn请求:- 无效化:DMA 设备的缓存行被标记为 Invalid,强制其将数据写回主存(若未完成)。

- 所有权转移:Host 的缓存行获得 Exclusive 或 Modified 状态,确保后续操作由 Host 独占

缓存行状态转换

- 设备侧:收到

SnpInvOwn请求后:- 若缓存行状态为 Modified:将数据写回主存,并标记为 Invalid。

- 若状态为 Exclusive/Shared:直接标记为 Invalid。

- Host 侧:在总线事务完成后:

- 若数据已写回主存:Host 缓存行状态为 Exclusive(与主存一致)。

- 若设备未写回(由协议决定):Host 可能直接从设备获取数据,状态为 Modified。

DMA 写入完成:设备通过 SnpInvOwn 将数据所有权转移给 Host,Host 无需手动刷新缓存即可读取最新数据。

内存屏障(也称内存栅栏、屏障指令)是一类同步屏障指令,强制CPU或编译器在屏障点之前的所有读写操作完成后,才能执行屏障点之后的操作

其核心作用包括:

- 阻止指令重排序:现代处理器和编译器为了提高性能会进行指令乱序执行(Out-of-Order Execution),内存屏障通过强制顺序执行避免由此引发的逻辑错误

保证内存可见性:确保一个线程对共享内存的修改能被其他线程及时观察到,避免读取到“脏数据

内存屏障主要应对以下两类问题:

-

缓存一致性问题

多核系统中,每个CPU核心有自己的缓存(Cache),可能导致不同核心看到同一内存地址的值不一致。例如:- Store Buffer延迟写入:CPU的写操作可能先存入Store Buffer而非直接写入缓存,其他核心无法立即感知变化

Invalidate Queues延迟失效:缓存行失效请求可能被暂存而未及时处理,导致读取旧数据

SnpInvOwn(Snoop Invalidate Own)是缓存一致性协议(如MESI)中的一种操作,用于标记某个核心独占缓存行并使其在其他核心中失效。此操作通常伴随内存屏障的原因如下:

- 保证失效操作完成:内存屏障强制将Store Buffer中的数据刷入缓存,并确保Invalidate消息被其他核心处理完毕,避免后续操作读取到失效前的旧数据

CXL.cache(缓存一致性协议):使CPU与加速器(如GPU/FPGA)共享缓存行级数据,支持原子操作和细粒度同步,消除传统PCIe架构中数据复制的开销

在多数情况下,为了提高系统性能,内存操作策略被配置为write back,write back策略大大减少了数据写到Memory的频率,大部分情况数据只保留在Cache中并在Cache中被更新。

CXL将硬件形式的Cache agent和Home agent内置于CPU之中,Host即可利用Cache agent和Home agent直接通过CXL BUS访问外设的Cache和Memory

但这需要BUS上每个处理器都要每时每刻监听总线上的变化,这无疑加深了处理器的负载

CXL的非对称协议(Asymmetric Protocol)是解决异构计算场景下缓存一致性问题的核心机制之一。其核心思想是通过主机集中管理缓存一致性,降低设备侧的设计复杂度,从而实现CPU与加速器、内存扩展设备之间的高效协作

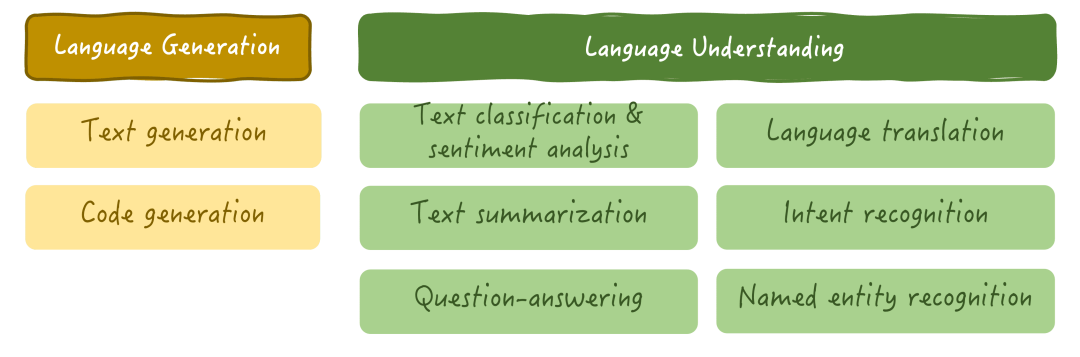

- CXL.io协议:继承并扩展PCIe 5.0/6.0的I/O协议,负责设备发现、配置和传统DMA操作。

- CXL.cache协议:定义设备与主机之间的缓存一致性交互,支持请求-响应机制(如缓存行状态查询、更新通知)。

- CXL.mem协议:允许主机以Load/Store指令直接访问设备内存,实现内存池化

这三个协议通过Flex Bus机制共享PCIe物理层(PHY),链路层动态复用数据流

减少设备侧负担

设备仅需实现轻量级的缓存代理(Cache Agent),无需处理复杂的全局一致性逻辑。例如,当GPU修改缓存数据时,只需通知主机侧的Home Agent,由主机完成全局状态更新和广播

主机集中控制一致性

在非对称架构中,缓存一致性代理(Home Agent)仅部署在主机(CPU)侧,由主机统一管理所有外设(如GPU、FPGA)的缓存状态

- Modified:数据被设备修改且未写回内存时,主机通过Snooping机制广播失效信号。

- Exclusive:数据仅存在于一个设备缓存中,允许直接修改。

- Shared:数据存在于多个设备缓存,需通过主机协调写操作。

- Invalid:缓存行无效,需从主机或其他设备获取最新数据。

CCIX(对称)

- 对等一致性:所有设备(如CPU、加速器)均需实现Home Agent和Cache Agent,平等参与缓存一致性管理

加速器可直接访问其他设备的缓存,但需通过复杂的侦听协议(Snoop Protocol)维护一致性

共享虚拟内存模型:数据通过虚拟地址(VA)在设备间自动同步,无需软件干预,但需要所有设备支持一致性代理

CXL

- 简化设备端设计:设备仅需支持CXL.cache或CXL.memory协议,无需独立的一致性代理,适合异构加速器(如GPU、FPGA)低成本接入

协议分层复用:基于PCIe 5.0/6.0物理层,兼容现有PCIe生态,支持动态复用CXL.io(I/O)、CXL.cache(缓存访问)、CXL.mem(内存访问)协议

CXL

- 统一内存池:主机可透明访问设备内存(CXL.mem协议),支持内存扩展和池化,例如将多个设备的DRAM整合为逻辑统一内存

- CXL.cache 允许设备缓存主机内存,使用MESI一致性协议,这对于需要频繁访问主机内存的加速器(如GPU或FPGA)非常重要。

- CXL.mem 使得主机可以像访问本地内存一样访问设备的内存,支持主机管理的设备内存(HDM)

Type 3设备的核心功能是扩展内存带宽和容量,例如连接DRAM、持久内存或其他存储介质。这类设备的主要角色是提供附加的存储资源,而非作为计算密集型加速器(如GPU或FPGA)执行需要缓存主机内存的操作。

CXL.cache协议的核心是允许设备主动缓存主机内存(例如通过MESI一致性协议优化访问效率)。而Type 3设备作为被动存储扩展单元,其内存由主机直接管理(通过CXL.mem协议),自身不需要主动缓存主机内存或维护复杂的缓存一致性状态。

-

Type 3设备支持多级内存(如高性能DRAM与高容量持久内存混合使用),其设计目标是通过灵活的物理拓扑提供存储资源,而非与主机共享缓存。主机通过CXL.mem协议直接管理设备内存,无需设备端缓存介入。

总结:Type 3设备的功能专注于内存扩展,不涉及需要缓存主机内存的场景,因此无需实现CXL.cache协议。这种设计权衡降低了复杂性,使其更高效、低成本地满足存储扩展需求。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)