ptpx功耗分析——分析功耗报告

pre netlist和post netlist会存在在同样的hierarchy中同样的instance的部分cell一样,即使门级仿真不带任何时序(也就是和rtl仿真一样,为理想状态下的仿真),ptpx跑功耗时也不带任何时序反标,输入输出的波形变化相同,同一个cell的pre和post的功耗也会存在差异,因为相同cell的输入状态(如input_net_transition)和输出状态(outp

前面记录了如何跑出正确的功耗数据,有了正确的功耗数据后需要对其进行分析。分析功耗数据首先需要看懂数据报告中的int power、switch power、leakage power都是什么,怎么获得的;其次有一定的分析方法;再次需要懂设计,而懂设计也在功耗优化中十分重要。

1 功耗数据的获得

估计芯片的功耗依据的是库文件的功耗数据和提供的波形文件,而库文件的功耗数据来自fab厂提供的库文件。对于对库文件的理解和熟悉的重要性在备注1里可见。

2 功耗数据中的int power、switch power、leakage power

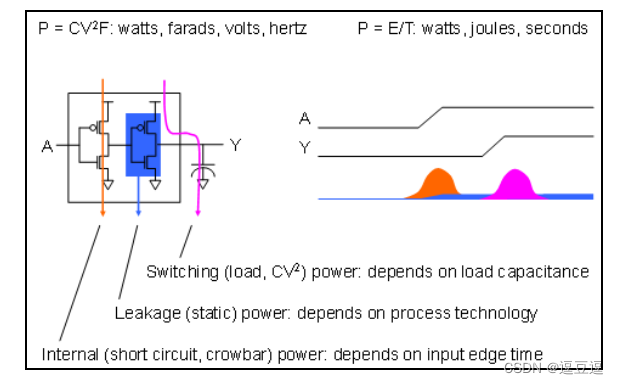

一个cell的功耗组成如图1(引用来自于DC的使用手册)和图2(引用自spyglass的使用手册)所示。三种功耗数据中就leakage power清晰简单一点,先从leakage power开始,后面在谈论int power和switch power。

图1 cell的功耗图

图2 cell的功耗图

2.1 leakage power

leakage pwoer一般叫做静态功耗,即电路处在有电源供电,该功耗主要由芯片电路的漏电功耗引起,因此又被称作漏电功耗。芯片主要由各种半导体电路组成,而半导体电路在被供电时就一定存在漏电流,因此也就一定存在漏电功耗。而在实际工程中是将电路的输入输出是否变动作为功耗分类的参考,即输入在变化时的功耗成为电路的动态功耗,而输入处于静止不变时的功耗成为静态功耗,因此有如下的表示:

静态功耗=leakage power=leakage_power.lib x static_probability=

在使用的库文件中的.lib文件中包含了每个cell处于具体某一种状态的leakage power。因此cell的leakage power为该cell在每种状态下的leakage power的总和,而static_probability由工具根据输入的波形文件统计出来的,即波形文件和波形截取时间一致(即是同一个case的同一个事件起点到同一个事件终点相同的时间长度T和相同的信号状态变化,任何一个不满足都不叫作“一致”),则静态功耗一致。

关于leakage power的理论可以参考如下链接和书籍:

(数字IC)低功耗设计入门(一)——低功耗设计目的与功耗的类型 - IC_learner - 博客园 (cnblogs.com)

《电子技术基础——模拟部分》(第五版 康华光)——了解基础的半导体器件的工作原理也静态功耗的来源基础

关于leakage power在芯片研发阶段的功耗解读可参考如下链接:

芯片功耗分析_input duty_王_嘻嘻的博客-CSDN博客

2.2 int power和switch power

动态功耗=int power+switch power

internal power在库文件中有写,switch power在库文件中没有写,但两者均与信号的翻转有关,关于两者的计算和举例可参考如下链接:

芯片功耗分析_input duty_王_嘻嘻的博客-CSDN博客

关于internal power,库文件中有明确的查找表,里面标明了与internal power相关的因素,一般包括intput_net_transition和total_output_net_capacitence。

关于internal power(又称短路功耗)的计算:

这里的是指信号翻转的频率,与switch power中的

是有一点区别的。

关于switch power的计算有两个计算公式:

(1)

(2)

这两个公式是等价的,原因是表示信号在单位目标时钟周期里的翻转率,而

表示信号的频率。一个信号在单位时钟周期里翻转次数是其频率的两倍。

可参考如下链接:

3 功耗数据的分析方法

(1)按模块整理出功耗的int power、switch power、leakage power,如果时间充足可按照hierarchy一级一级的整理出三种功耗以及每一级对应的综合后的面积。将功耗和case对应分析,看看是否存在case中没有工作的模块却有相应的功耗,如果有功耗,对应波形文件在Verdi里打开看没工作的模块的时钟是否关闭,输入端口是否处于静态——可以采用clock gate的方案降低功耗。将功耗数据结合面积报告一起分析,看各模块的功耗和其面积是否一致,一般情况下面积和功耗成正比,如果不一致,则需要查看原因。

(2)将每个 模块的RAM和logic的三种功耗整理出来,看看RAM和logic的功耗占比,有利于查看功耗数据的正确性,同一块RAM的pre功耗和post功耗变化很小,这可以用于检查功耗数据的正确性,有利于提出功耗优化意见,比如将ram换成寄存器try,换不同厂家的ram,将stand cell换不同电压阈值(HVT\SVT\LVT\UHVT)或者不同电压阈值比例的stand cell进行try或者约束某个模块用某种stand cell。

(3)将post的网表进行无sdf的功耗分析,即在产生fsdb波形文件时不用sdf文件,在进行功耗分析时不用sdf文件。将有sdf的功耗数据和无sdf的功耗数据进行对比分析,两者的leakage power应该是一样的,而有sdf的iinternal power和switch power应该比没有sdf的功耗数据大,大的部分是由于加上延时后产生的glitch导致的。在设计时可以采用寄存器将glitch剔除,也可以用其它的方法(发现并消除互补相乘项,增加乘积项以避免互补项相加,在输出端并联电容)去除冒毛刺,见如下链接 和书籍数字电路基础知识—— 组合逻辑电路中的竞争与冒险(竞争与冒险、检验方法、及消除方法)_竞争冒险产生的原因以及如何消除_CLL_caicai的博客-CSDN博客

《电子技术基础——数字部分》(第五版 康华光)——了解数字电路工作的基础教材

一定要明确目标功耗,每一次的功耗报告结果均要与目标数据作比较。比目标数据大在哪里,为什么大,大的部分是否合理;比目标数据小在哪里,为什么小,小的部分是否合理。

推荐一个网址,该网址中关于power的文档对于初次接触功耗分析的入门很有帮助:spyglass power文档 - 数字IC设计讨论(IC前端|FPGA|ASIC) - EETOP 创芯网论坛 (原名:电子顶级开发网) -

4 懂设计的重要性

如果仅把自己定位于提供准确、正确功耗数据的人员,大可不必懂设计,只要确保前一级输出的网表、波形文件、延时文件一致、准确无误,工具设置的参数正确则跑出来的功耗就是正确的。但是不想被动的提供功耗数据,想为整个芯片降低功耗做出贡献、想往低功耗方向发展,还需要懂设计,需要从芯片全局整体出发考虑,这样才能更好的降低芯片的功耗。

====================备注 1============

做功耗分析还需要有lib库相关的知识储备、对PR有一定的了解,能有门级仿真的经验也会锦上添花。

打开库的.lib文件,认真了解里面的内容及相应的关系。在lib文件里会写出每个cell在的leakage power相对不同电源下各种输入状态下的值,不同的lib可能会有一定出入,但leakage power只与输入信号的状态和电源有关。会记录cell的internal power,会涉及相应的计算表的调用,该计算表会涉及相应的variables,如input_transition_time,total_output_net_capacitance、nosie传输等与cell前后级关系的变量,也就是说即使在pre和post中相同instance相同cell在相同的波形、电压激励下,功耗也会不同。lib里的output_voltage、timing、driving等都会写出计算时调用的表以及相应的变量。做好功耗分析熟知各功耗的意义以及其在工具里的计算方式是必备的功课。

====================备注 2============

pre netlist和post netlist会存在在同样的hierarchy中同样的instance的部分cell一样,即使门级仿真不带任何时序(也就是和rtl仿真一样,为理想状态下的仿真),ptpx跑功耗时也不带任何时序反标,输入输出的波形变化相同,同一个cell的pre和post的功耗也会存在差异,因为相同cell的输入状态(如input_net_transition)和输出状态(output_load)不一样,这里可以参见前面提到的三种power的计算和lib中的功耗相关的表查看。

此部分笔记暂记到此处吧,后期有补充再添上,如有侵权请告知,及时整改,谢谢!如有错误,欢迎各位网友友善指出,及时改正。

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)