XILINX ZYNQ仅有PL端(FPGA)逻辑资源的程序固化 / 烧录

XILINXZYNQ仅有PL端(FPGA)逻辑资源的程序固化刚开始接触ZYNQ是从PL端开发开始上手学习的,当时使用JTAG下载程序,断电重启后程序就没了,所以当时一直很纳闷怎么固化程序,后来又学习了PS端的开发,知道了ZYNQ需要在SDK里对程序进行固化。如何固化只用到PL资源的程序,写这样一篇文章为各位有疑惑的同学提供参考。一任务目标本文将对PL端编写的呼吸灯程序进行固化,程序烧录至QPSI中

XILINX ZYNQ仅有PL端(FPGA)逻辑资源的程序固化 / 烧录

刚开始接触ZYNQ是从PL端开发开始上手学习的,当时使用JTAG下载程序,断电重启后程序就没了,所以当时一直很纳闷怎么固化程序,后来又学习了PS端的开发,知道了ZYNQ需要在SDK里对程序进行固化。如何固化只用到PL资源的程序,写这样一篇文章为各位有疑惑的同学提供参考。

一 任务目标

本文将对PL端编写的呼吸灯程序进行固化,程序烧录至QPSI中。

硬件开发环境:正点原子领航者开发板 ZYNQ 7020

软件件开发环境:VIVADO 2018.3

二 Vivado环境下配置

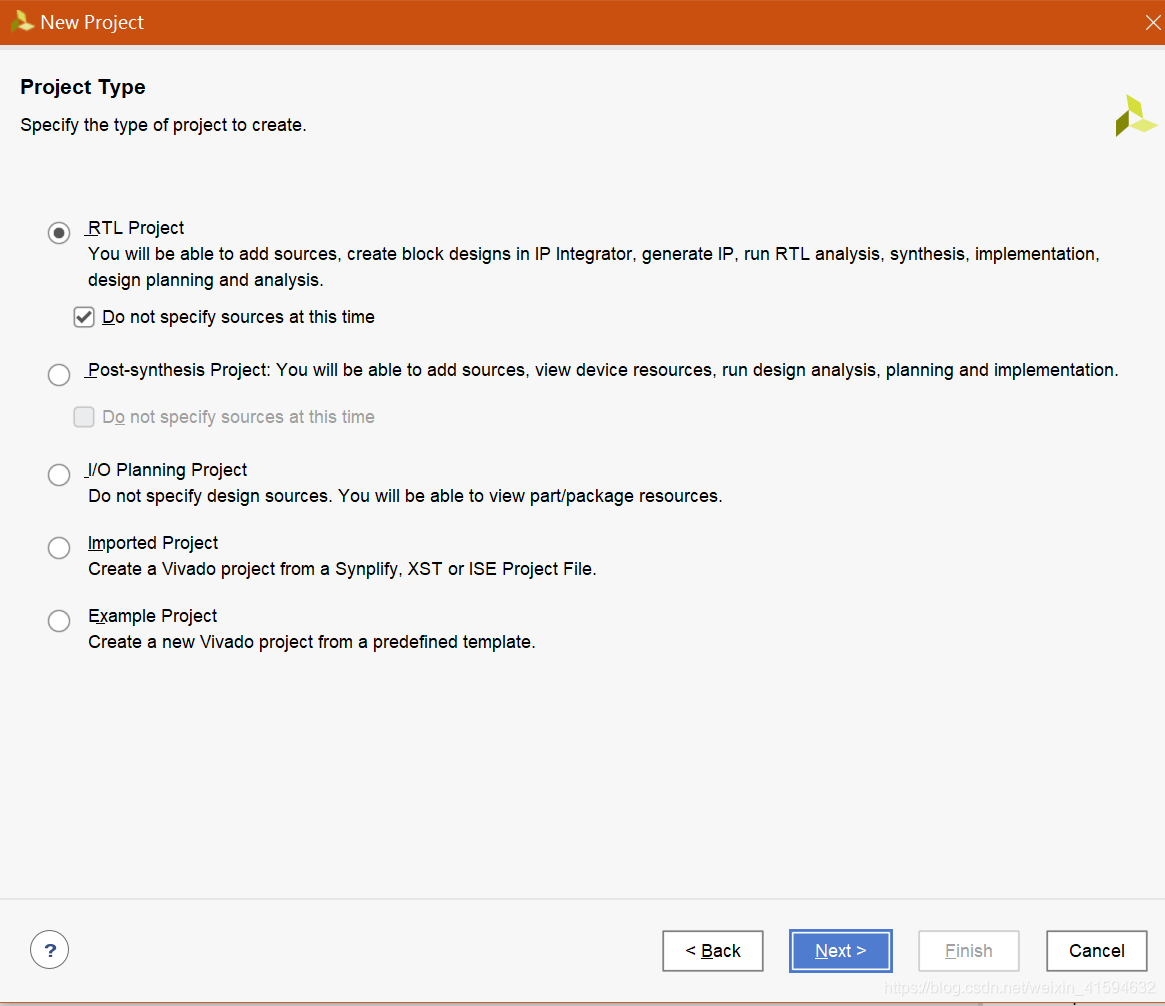

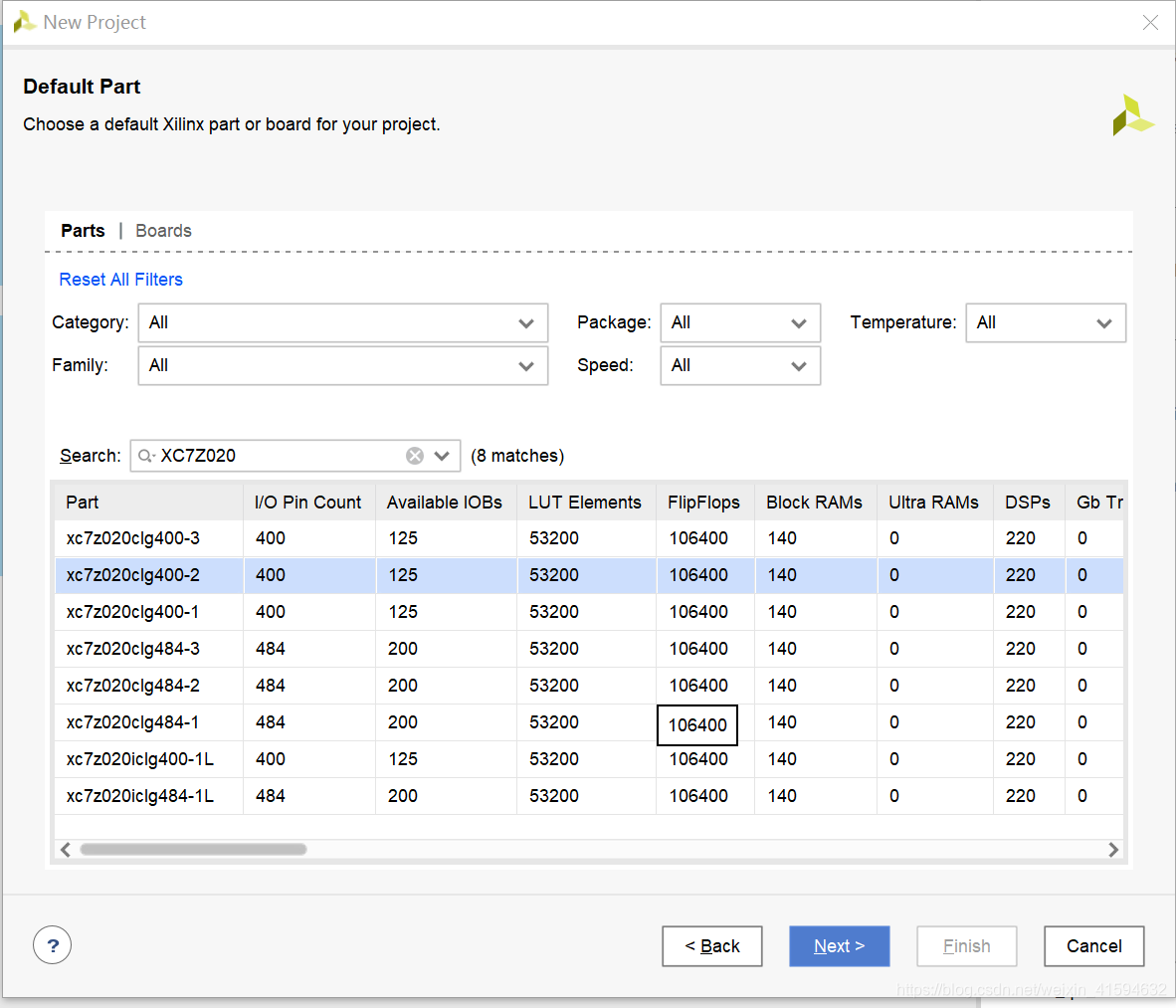

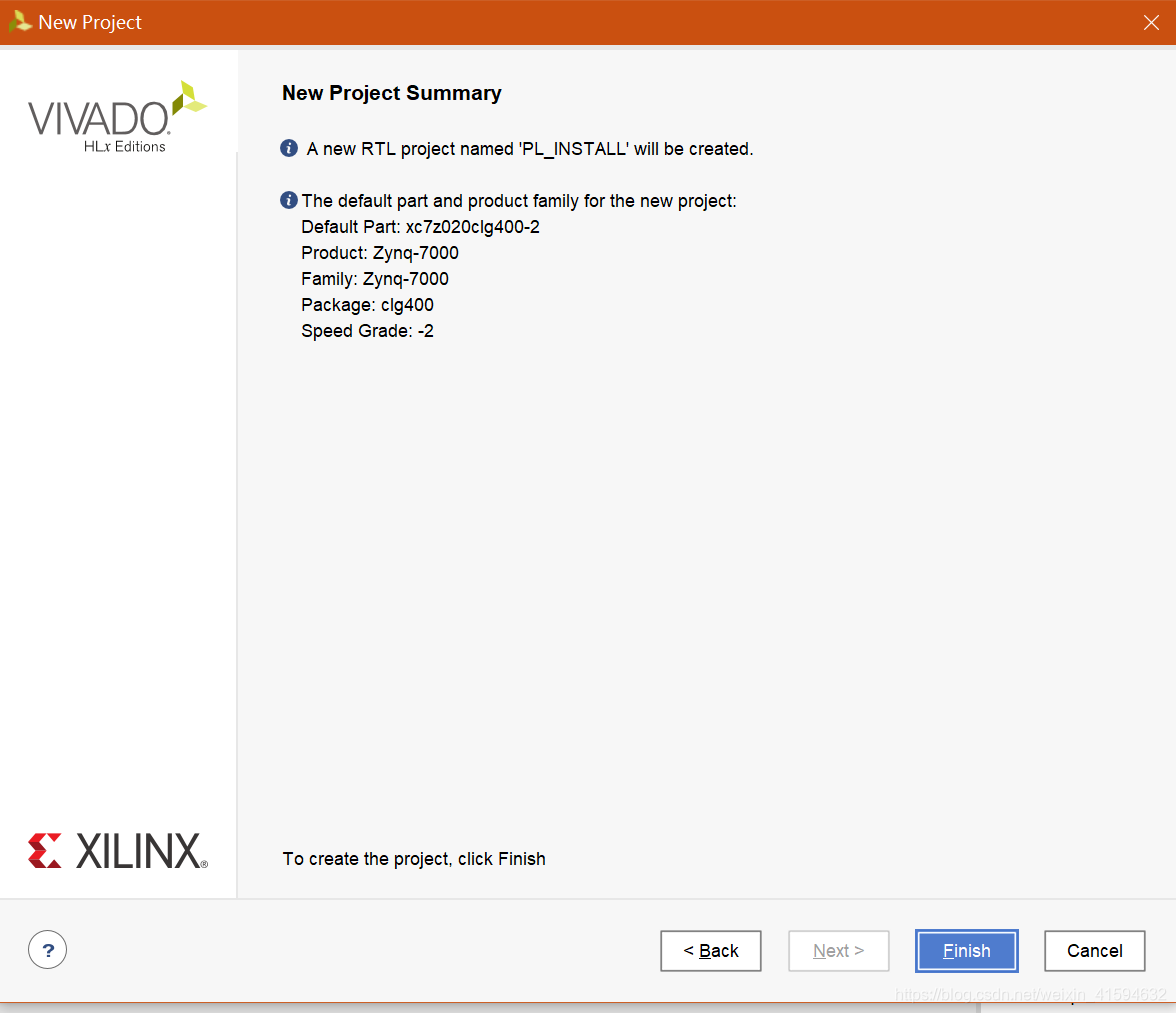

打开Vivado软件,新建工程,我命名为“PL_INSTALL”,下一步后选择"RTL Project",然后根据自己的板卡选择器件型号。

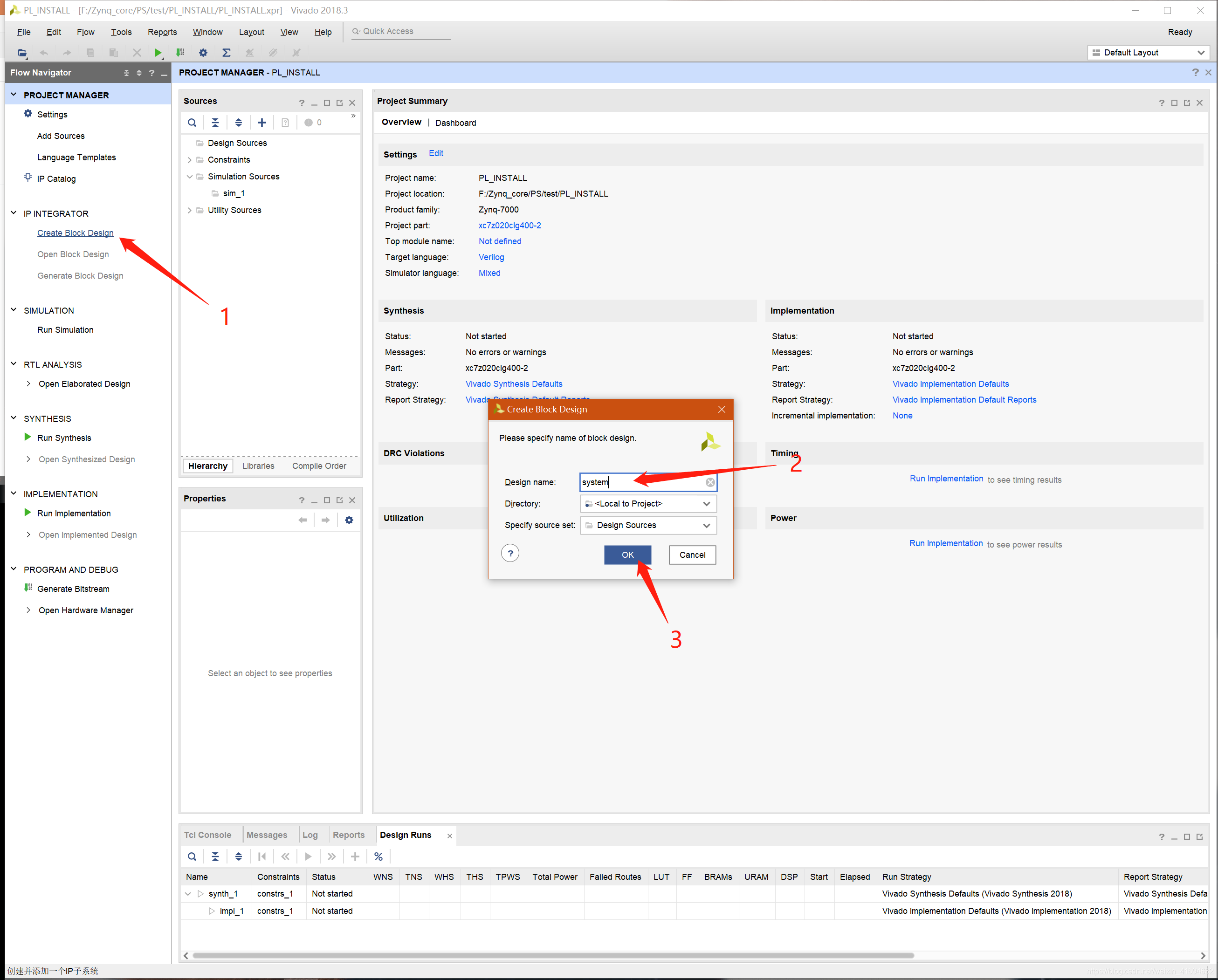

创建完成后,进入到开发界面,点击导航栏左侧的“Create Block Design”,新建名为“system”的模块设计。

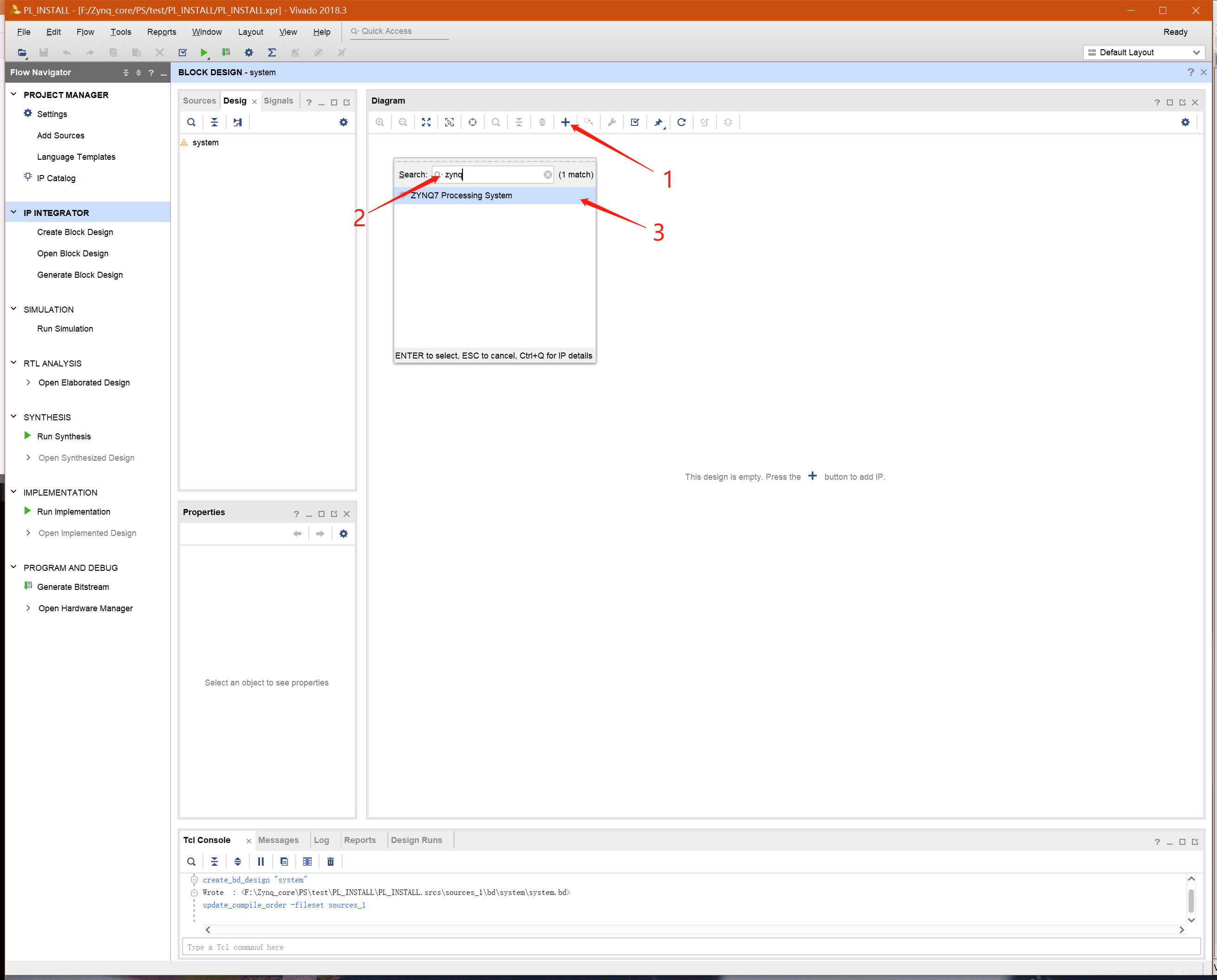

创建完成后,进入到“Diagram”界面,添加ZYNQ IP核。

双击添加后的IP核,进入到配置界面。首先打开QSPI外设。

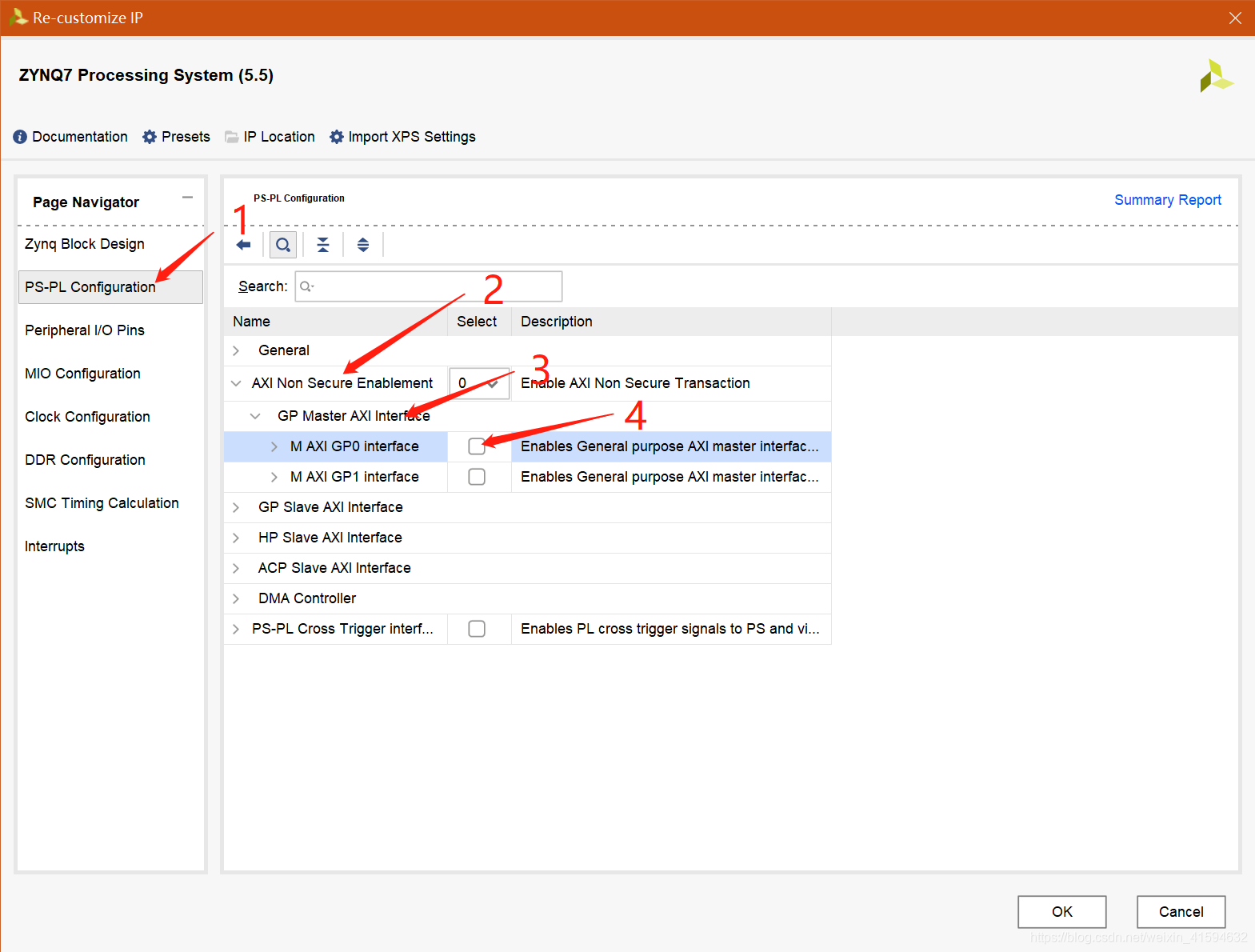

因为在本文的固化程序实验中,没有用到AXI的接口,因此我们需要将AXI接口取消掉。不然的话如果在仿真时AXI接口还是悬空的状态系统就会报错。

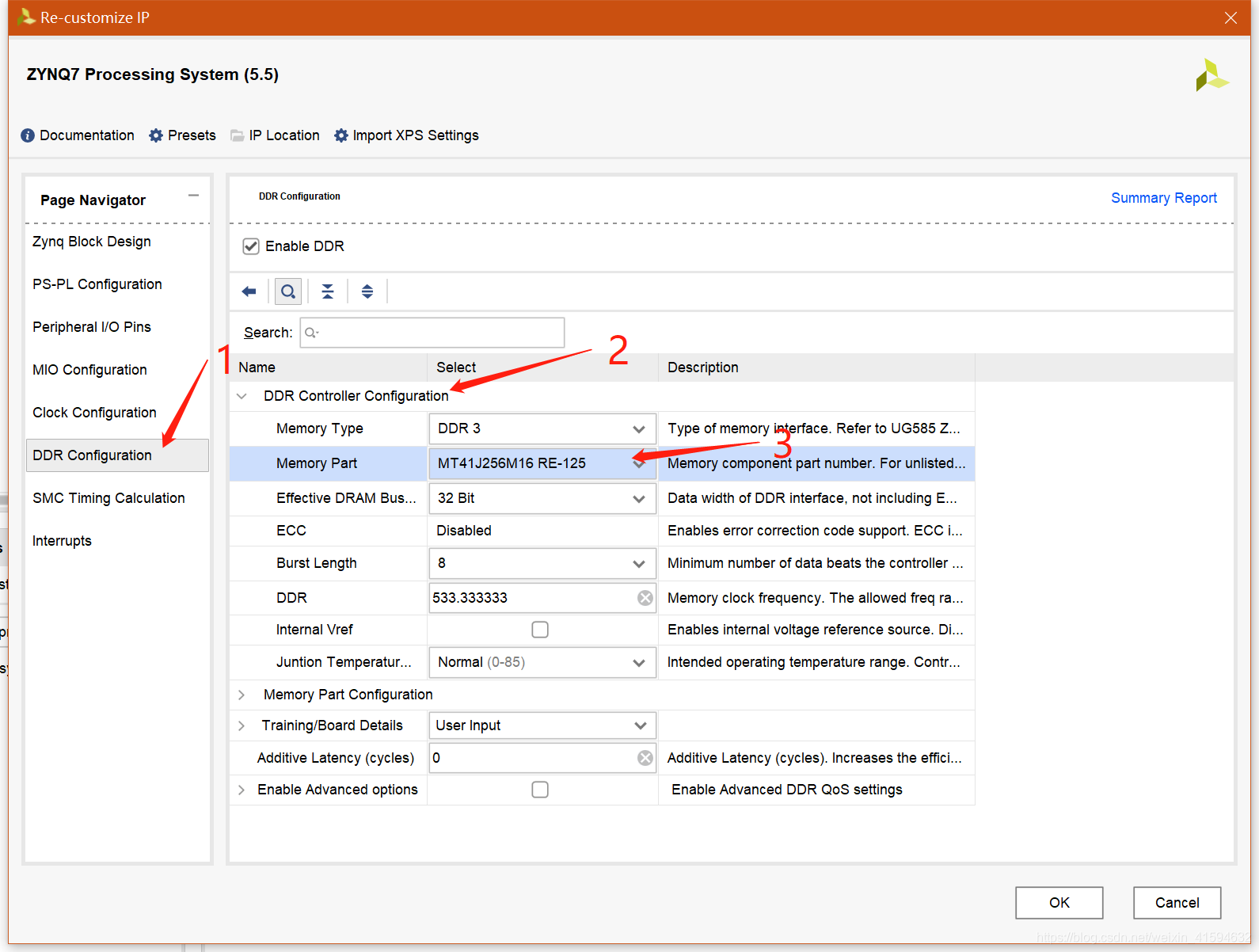

下面配置DDR3

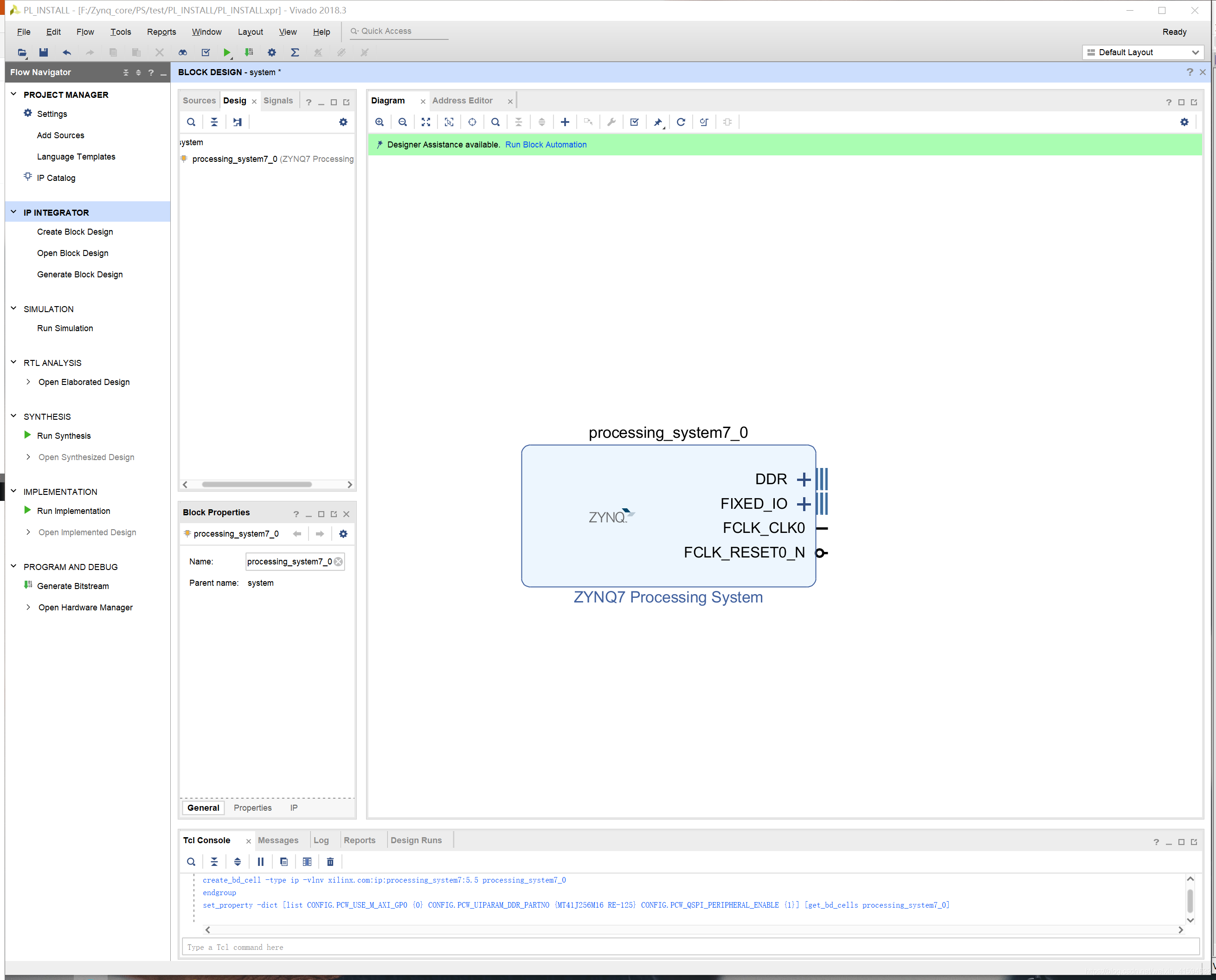

最后点击OK,结束对IP核的配置。

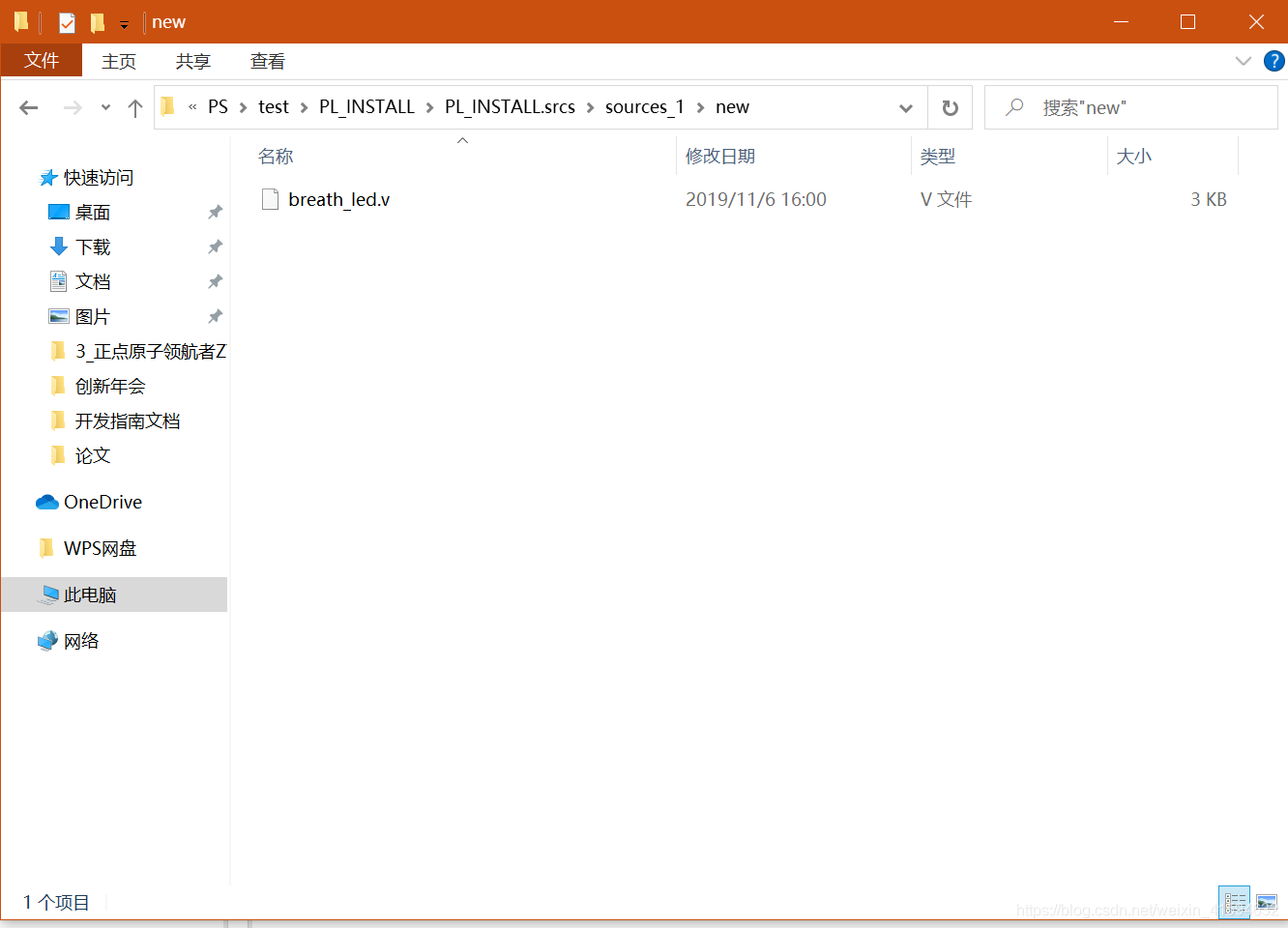

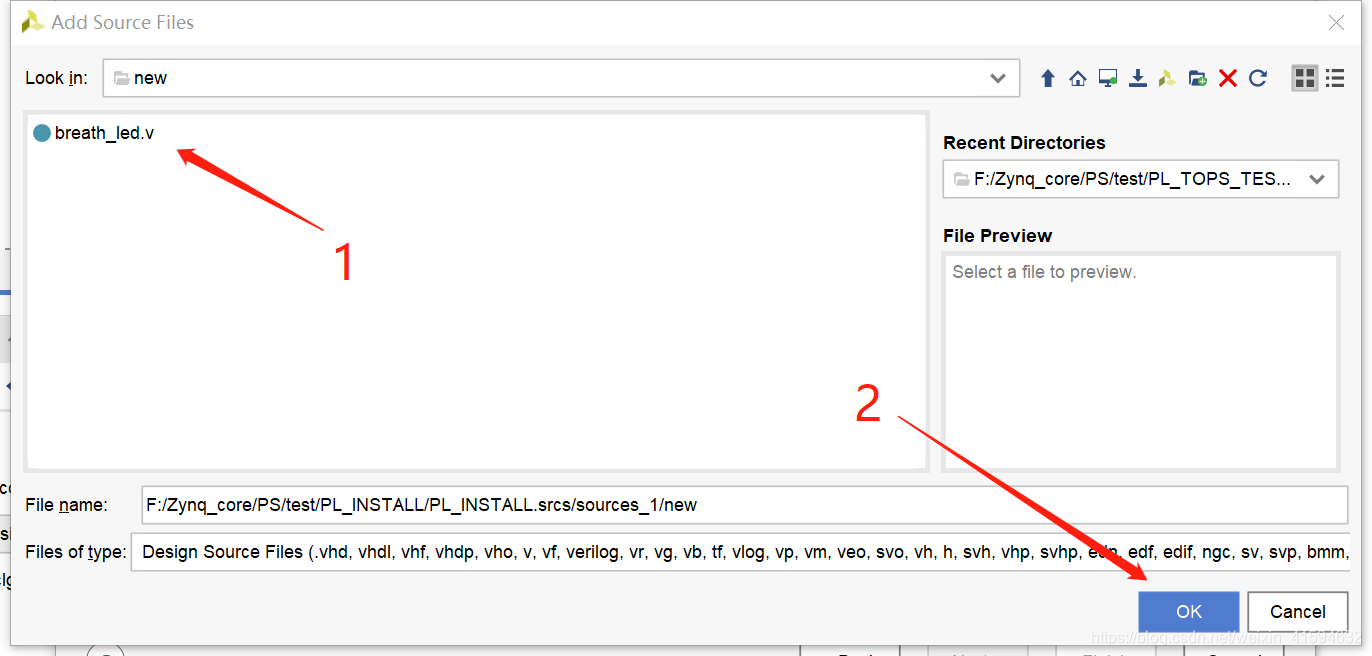

接下来需要将我们要固化的.v文件添加进来。打开工程文件夹中的.srcs文件夹,在sources_1文件夹下新建一个new文件夹,然后把.v文件拷贝进来。在这里我选了一个之前写好的LED呼吸灯程序

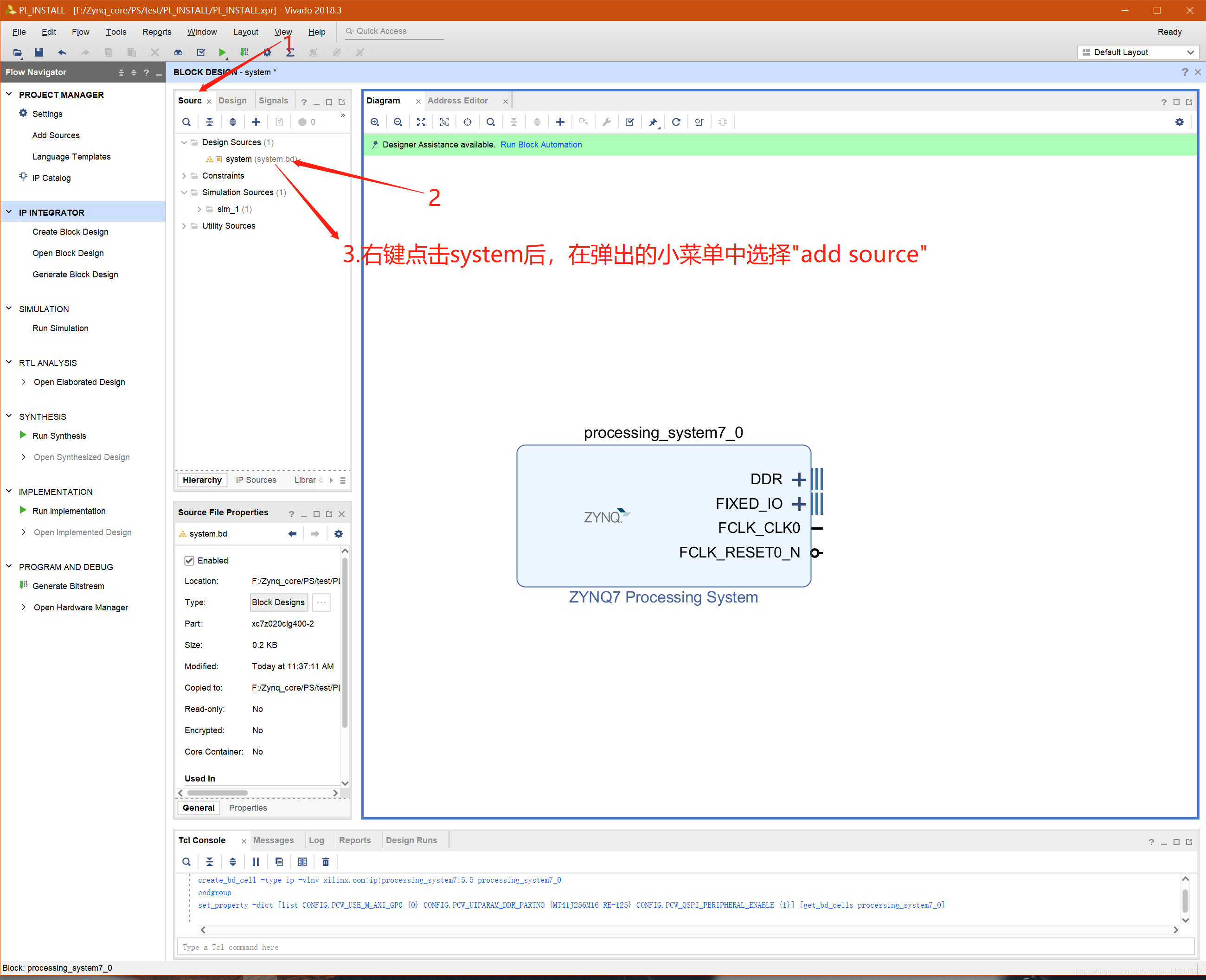

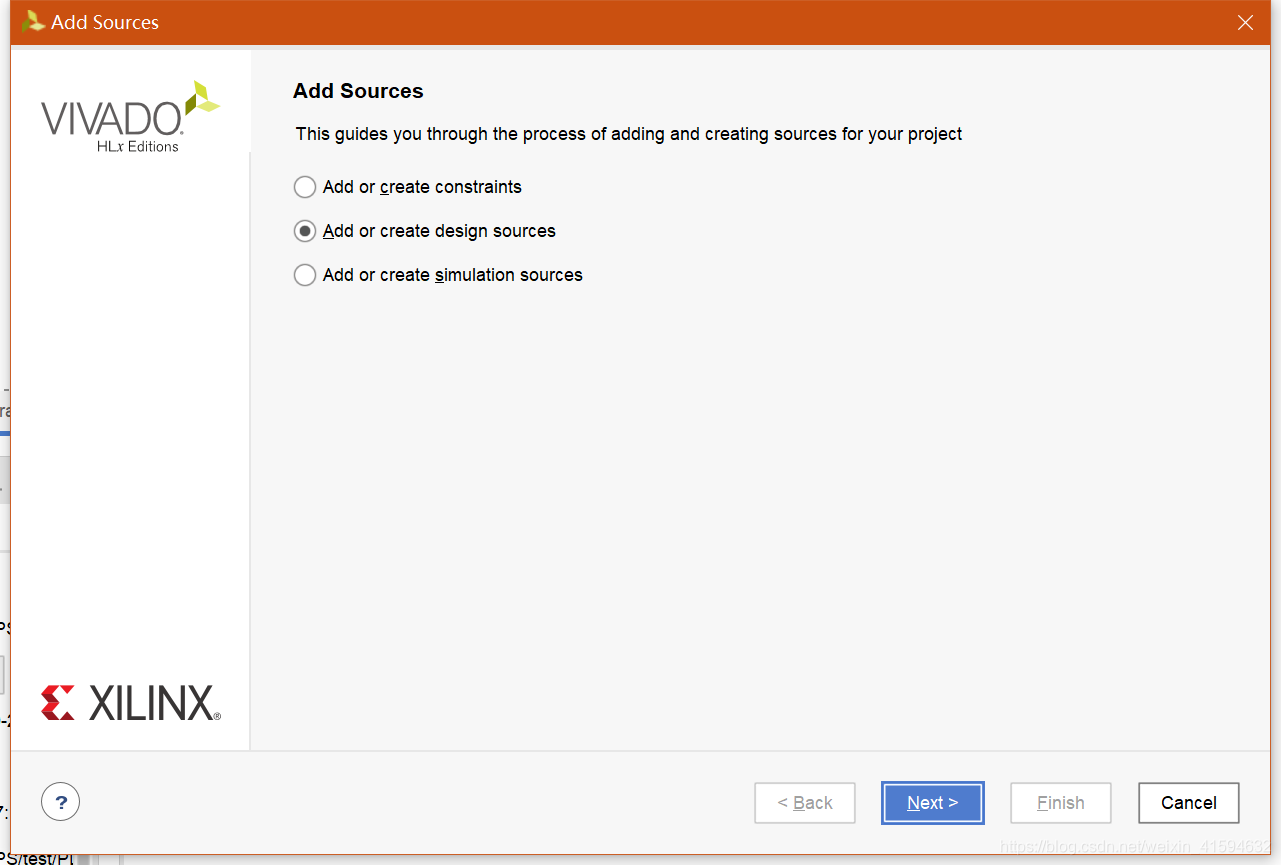

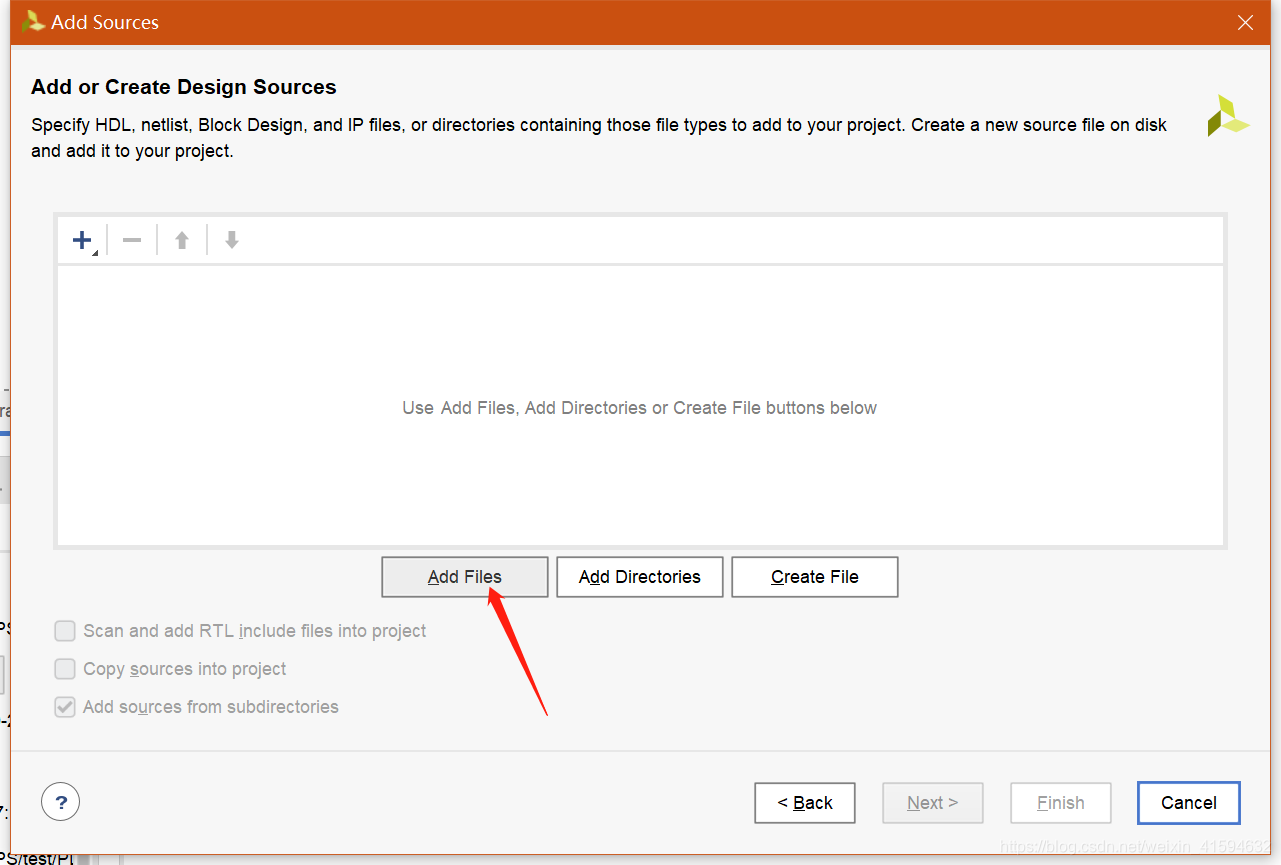

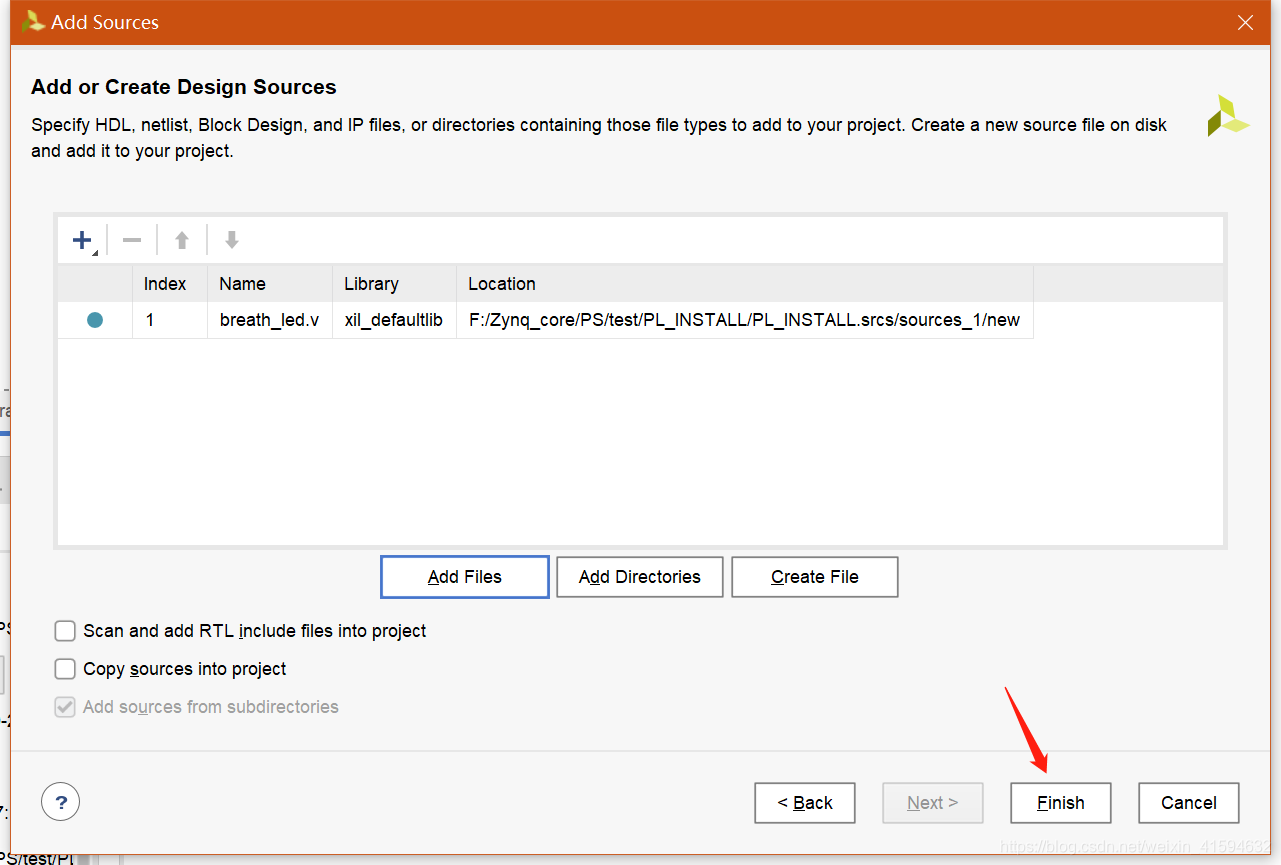

拷贝好之后,在vivado中添加这个.v文件

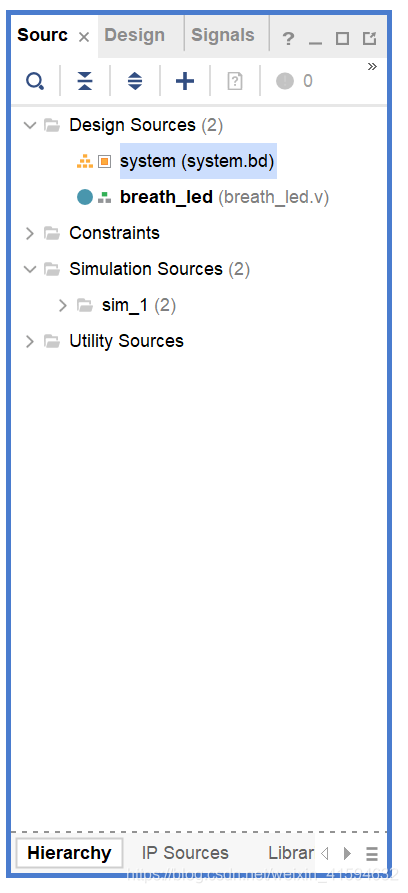

可以看到,Source页面中新增了我们添加的.v文件,即添加成功。

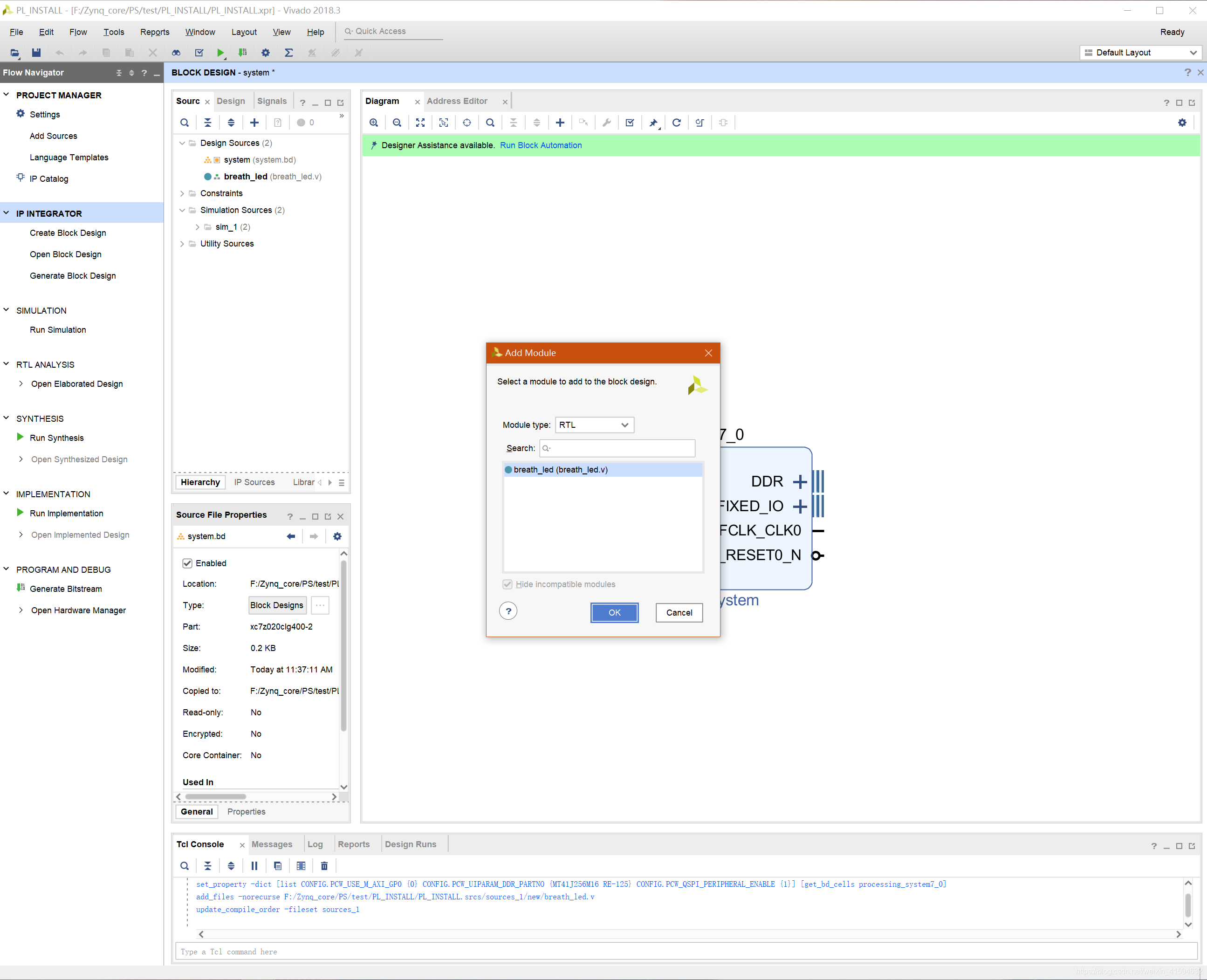

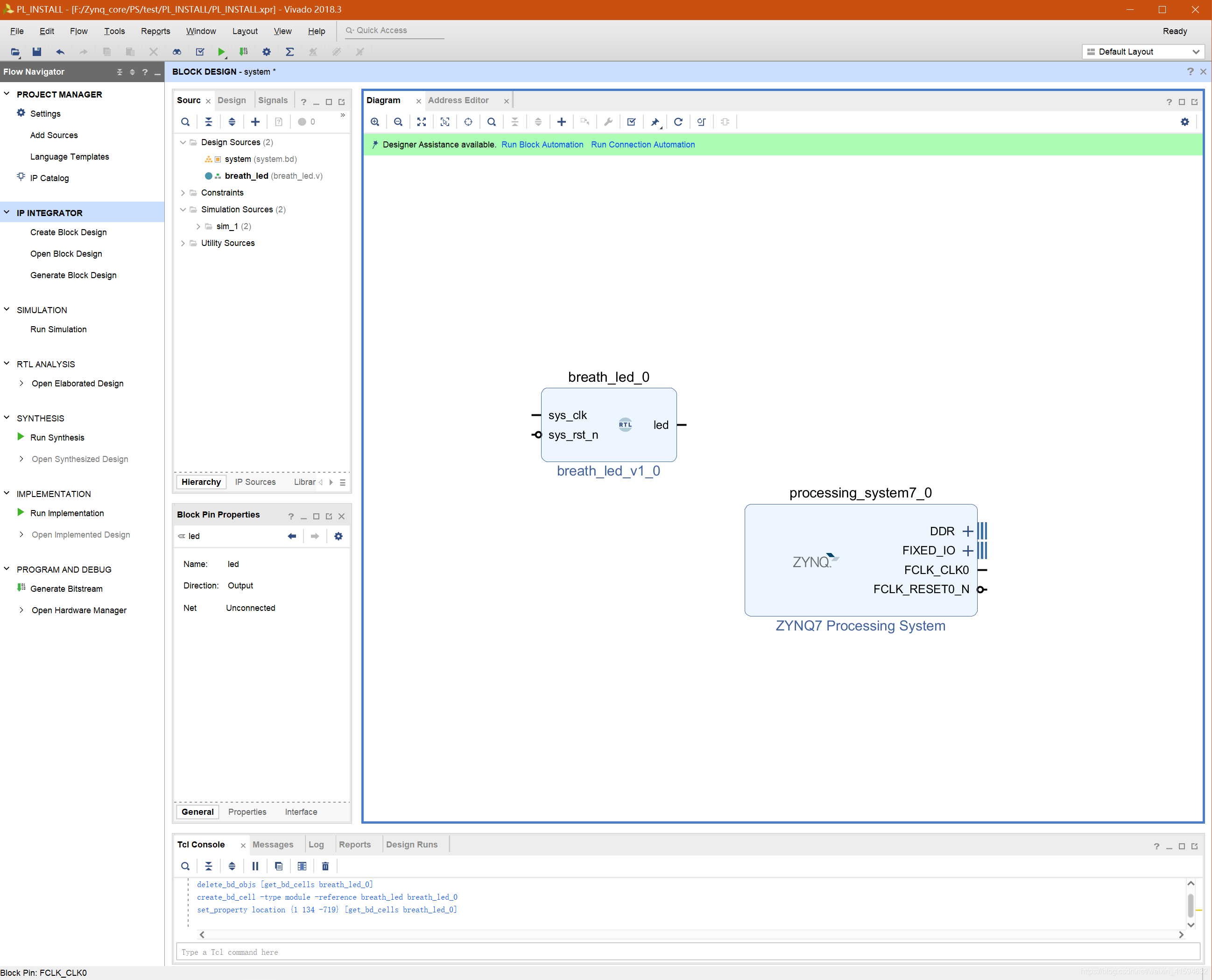

接下来在Diagram视图中的空白处右键,选择"Add Moudle"选项,把刚才添加.v文件以模块的形式添加进来。

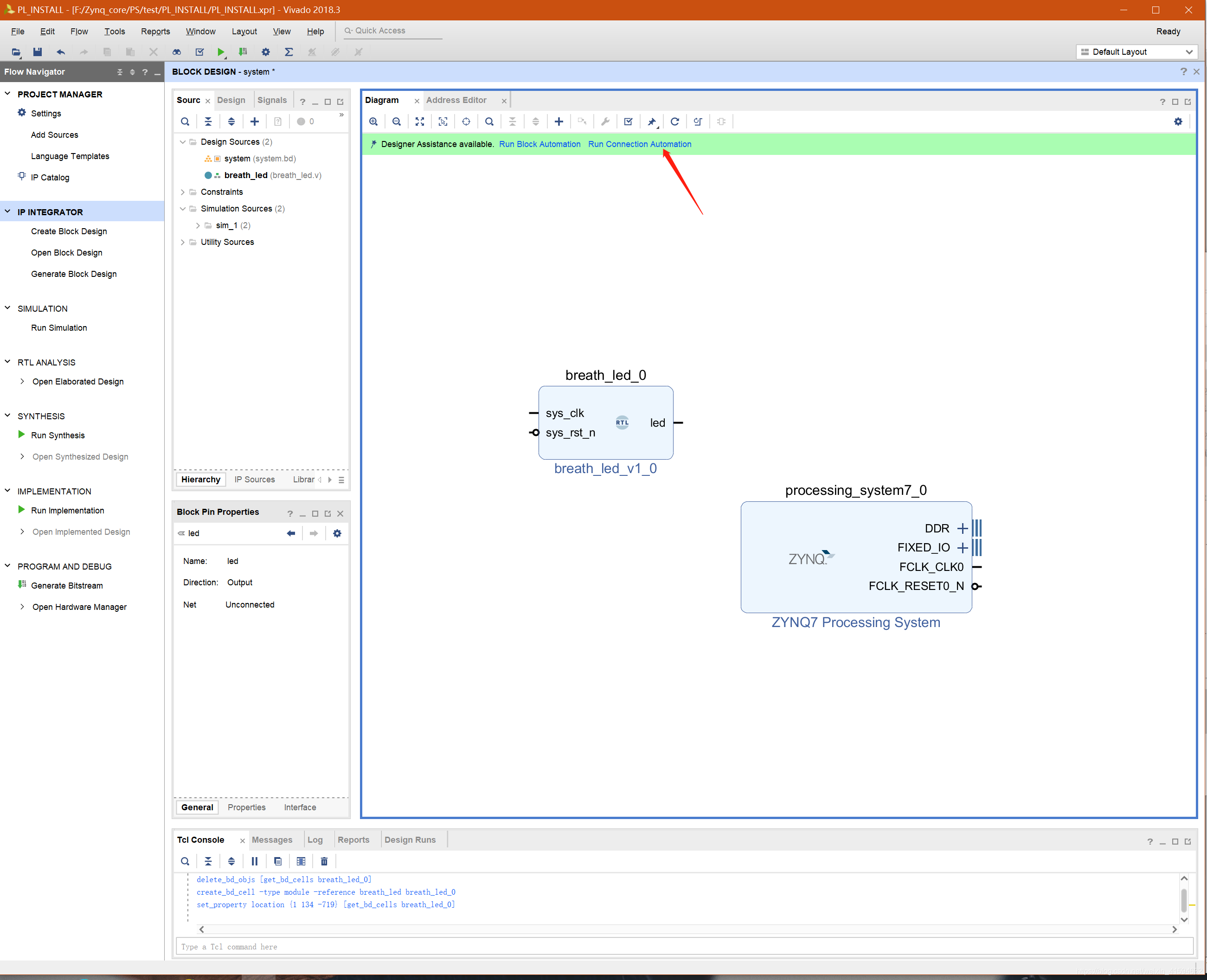

然后进行自动连线

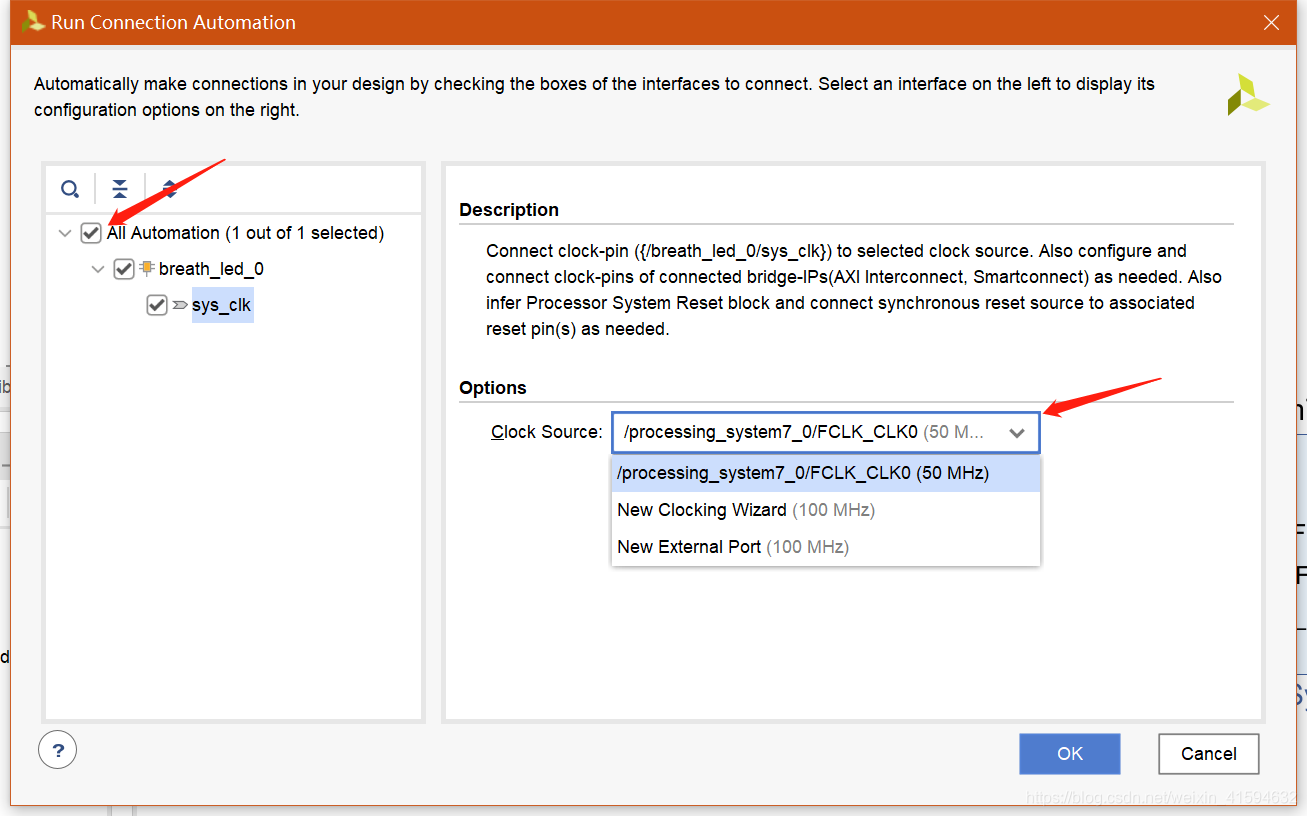

勾选全部模块自动连线,然后在时钟源配置界面选择ZYNQ FCLK端口提供的50MHZ时钟。

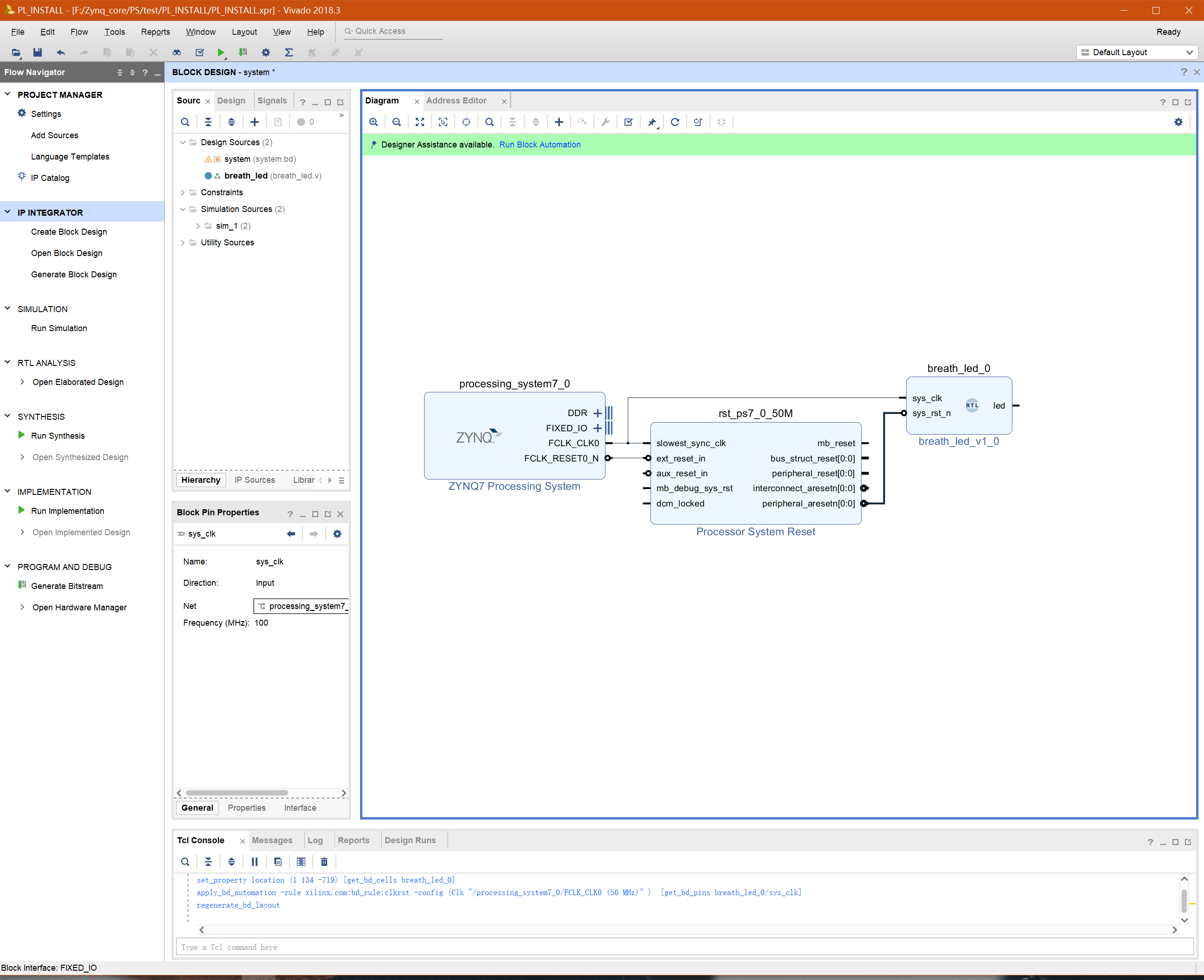

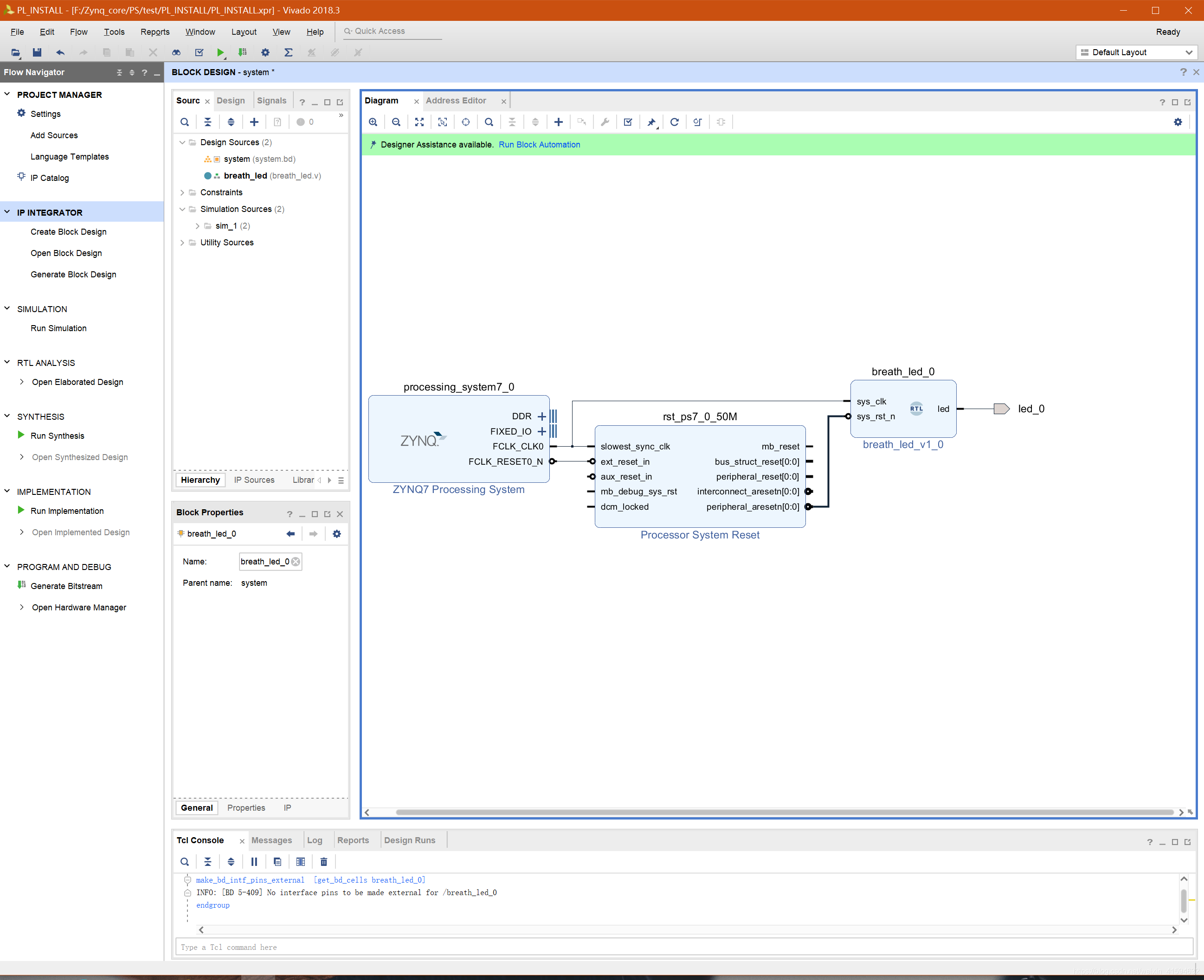

布线完成后如下图所示

我所添加的模块只有一个输出端口“led”,我们需要右键模块中的led端口,然后选择"Make External"选项。

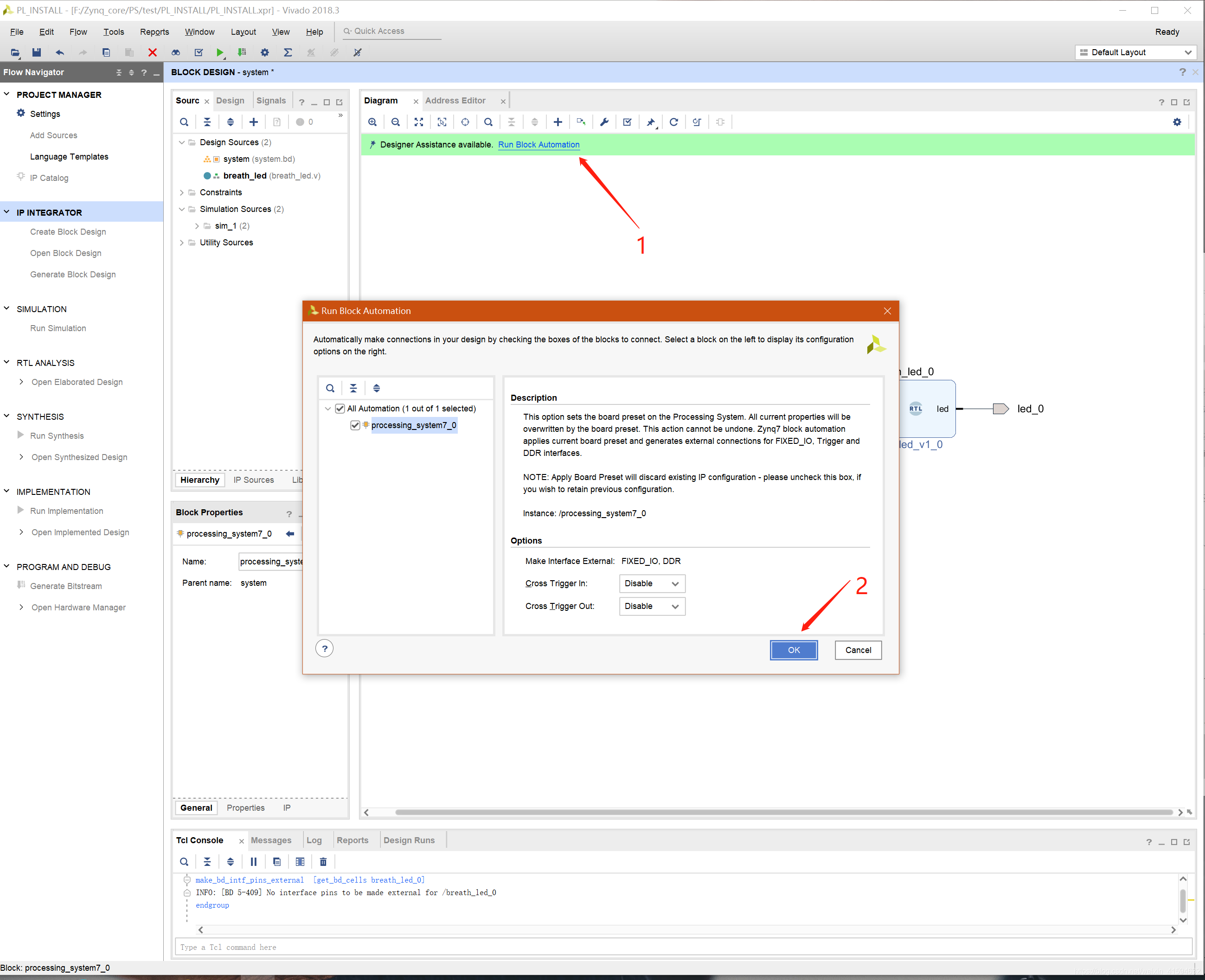

完成后,点击"Run Block Automation"

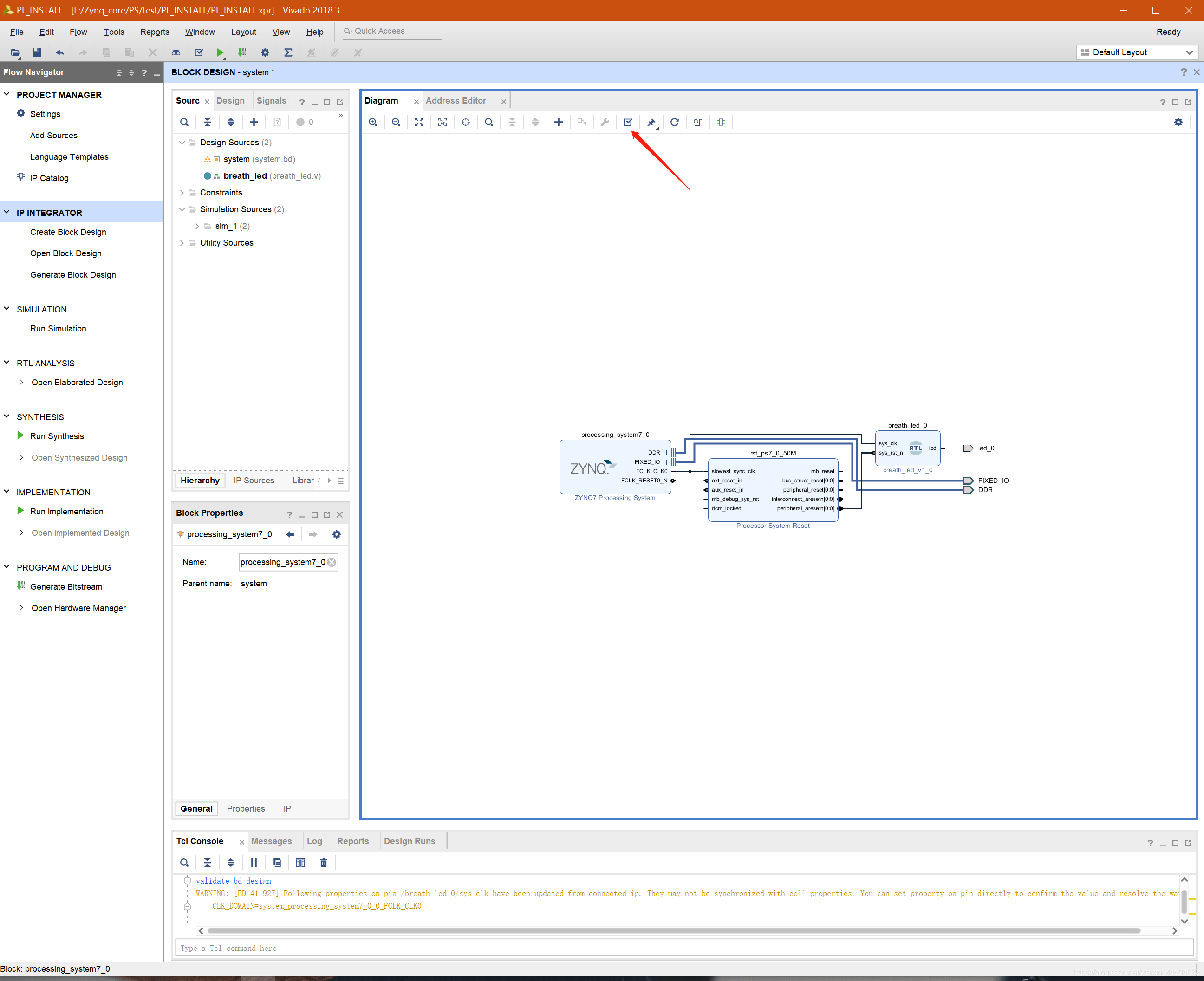

完成后,进行仿真验证

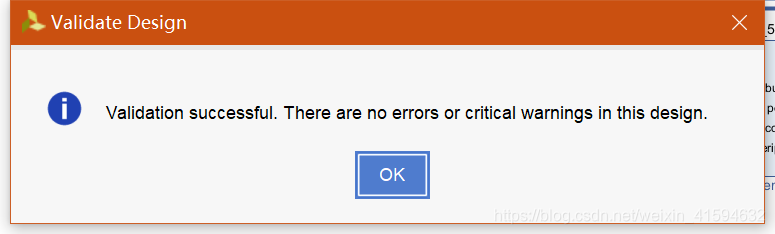

弹出如下窗口则设计无误。

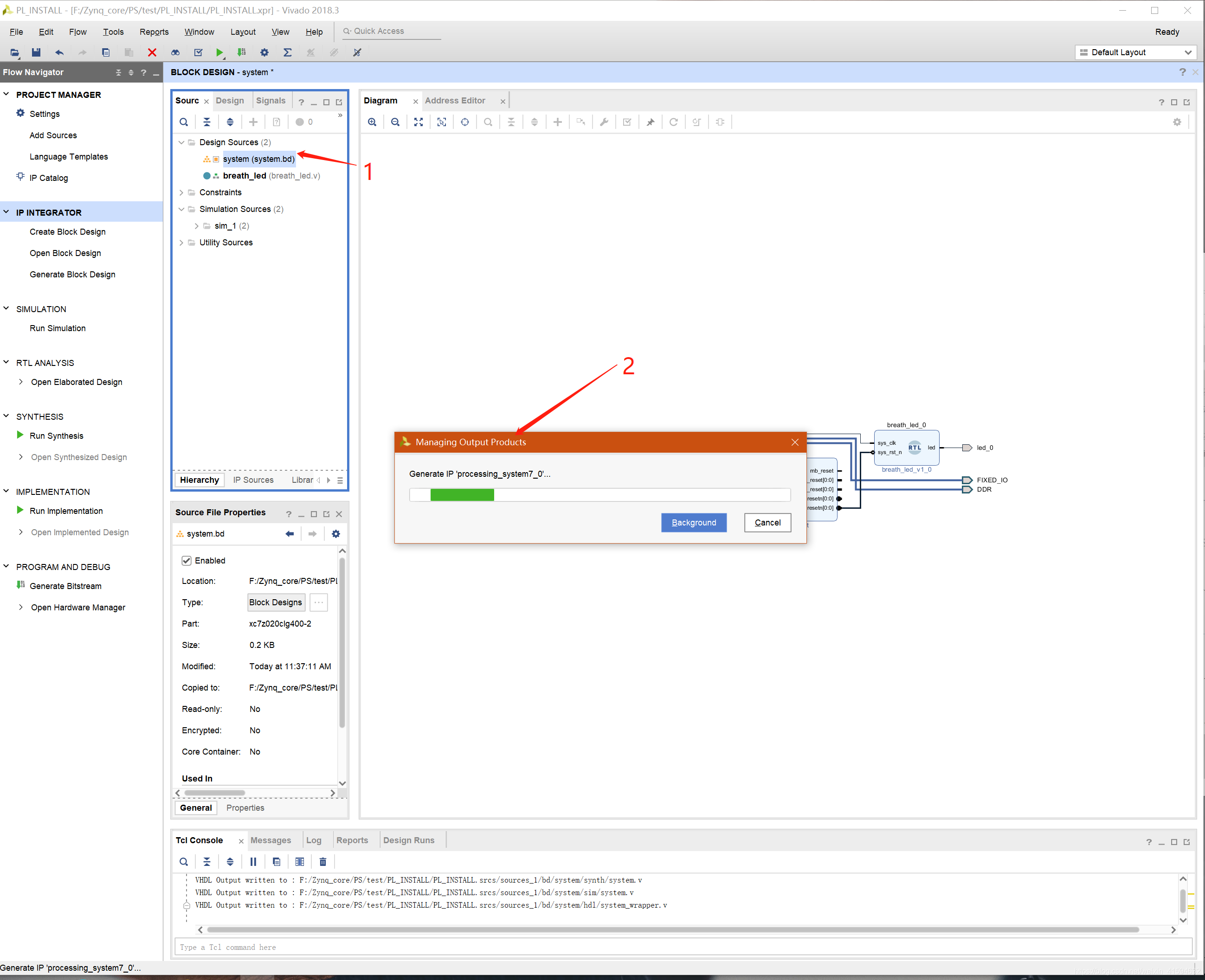

右键“system”后,选择“Generate Output Products”选项

完成后,弹出如下窗口

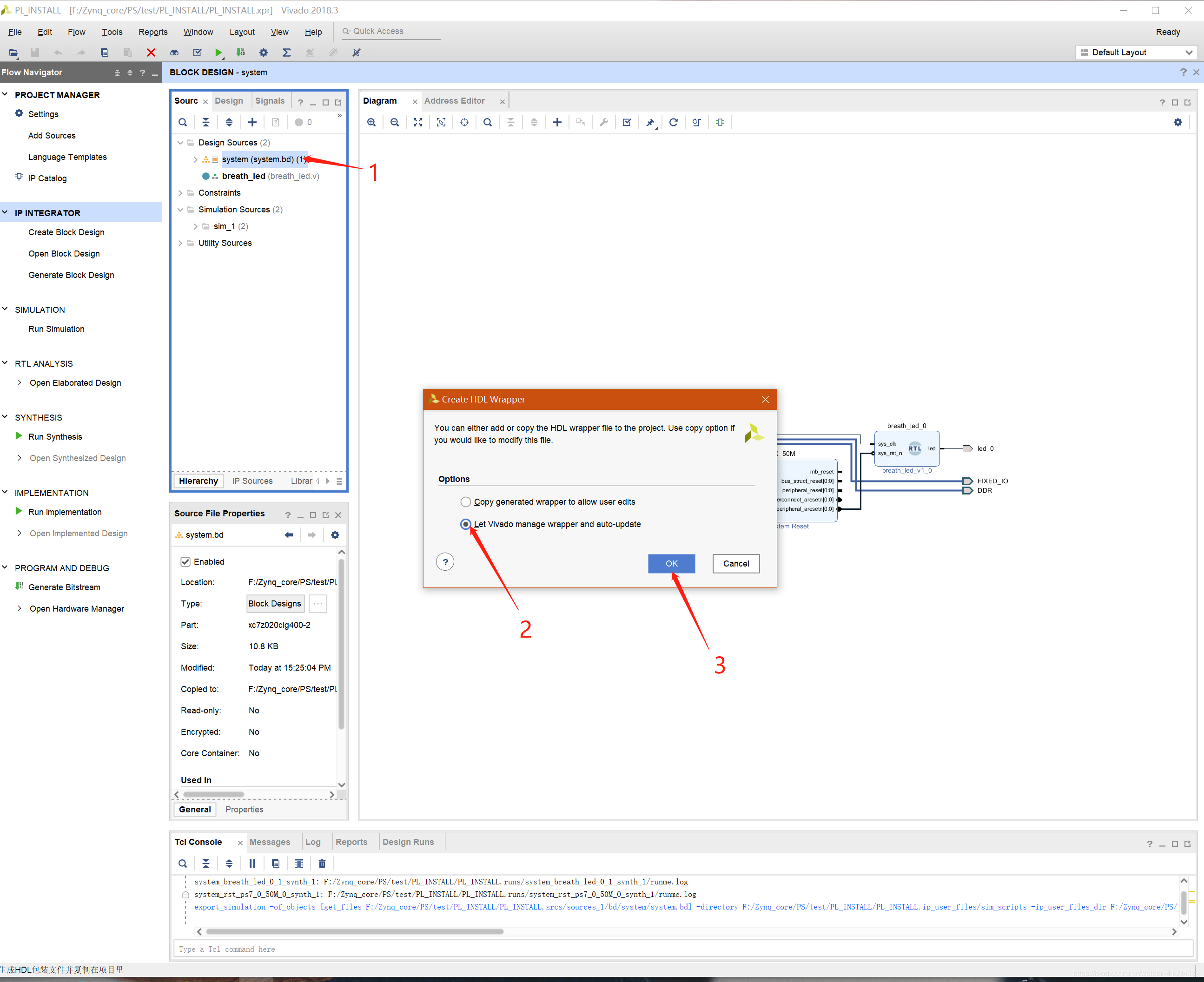

然后还是右键“system”,这次选择“Create HDL Wrapper”选项

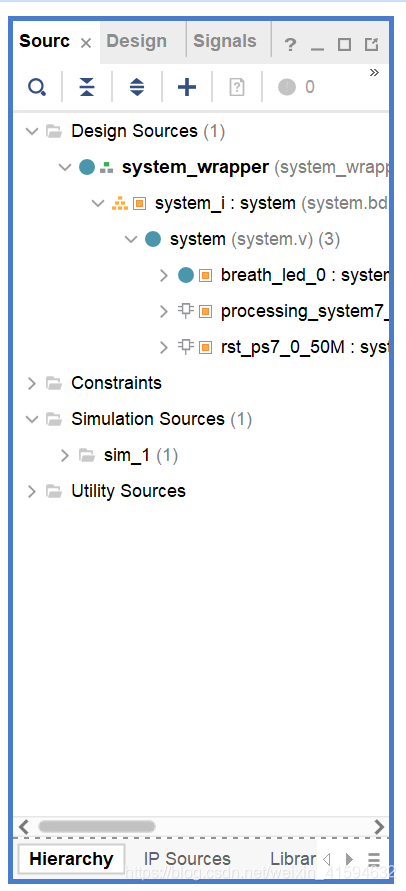

完成后,Source栏里会生成一个顶层文件

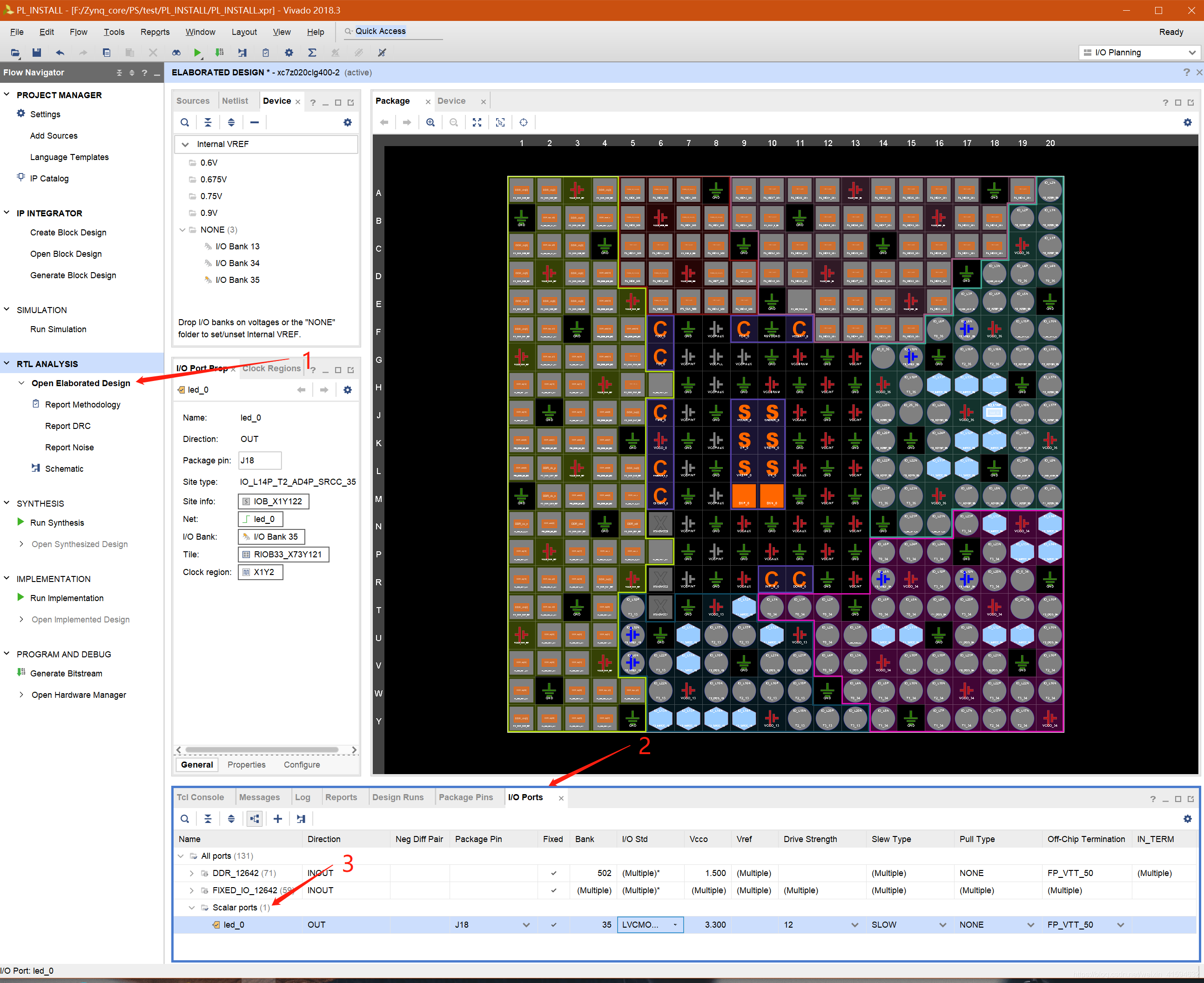

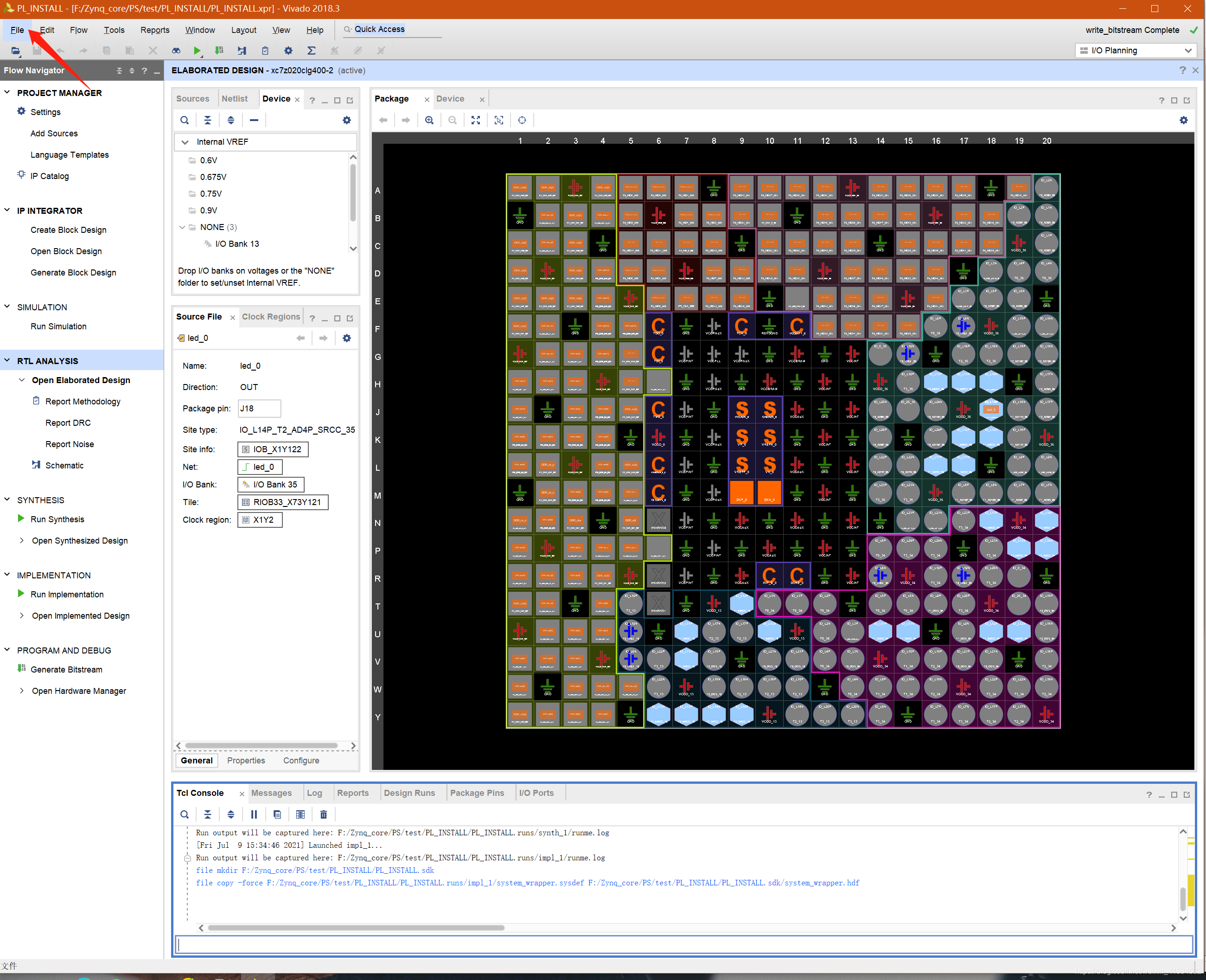

下面我们对IO引脚进行分配

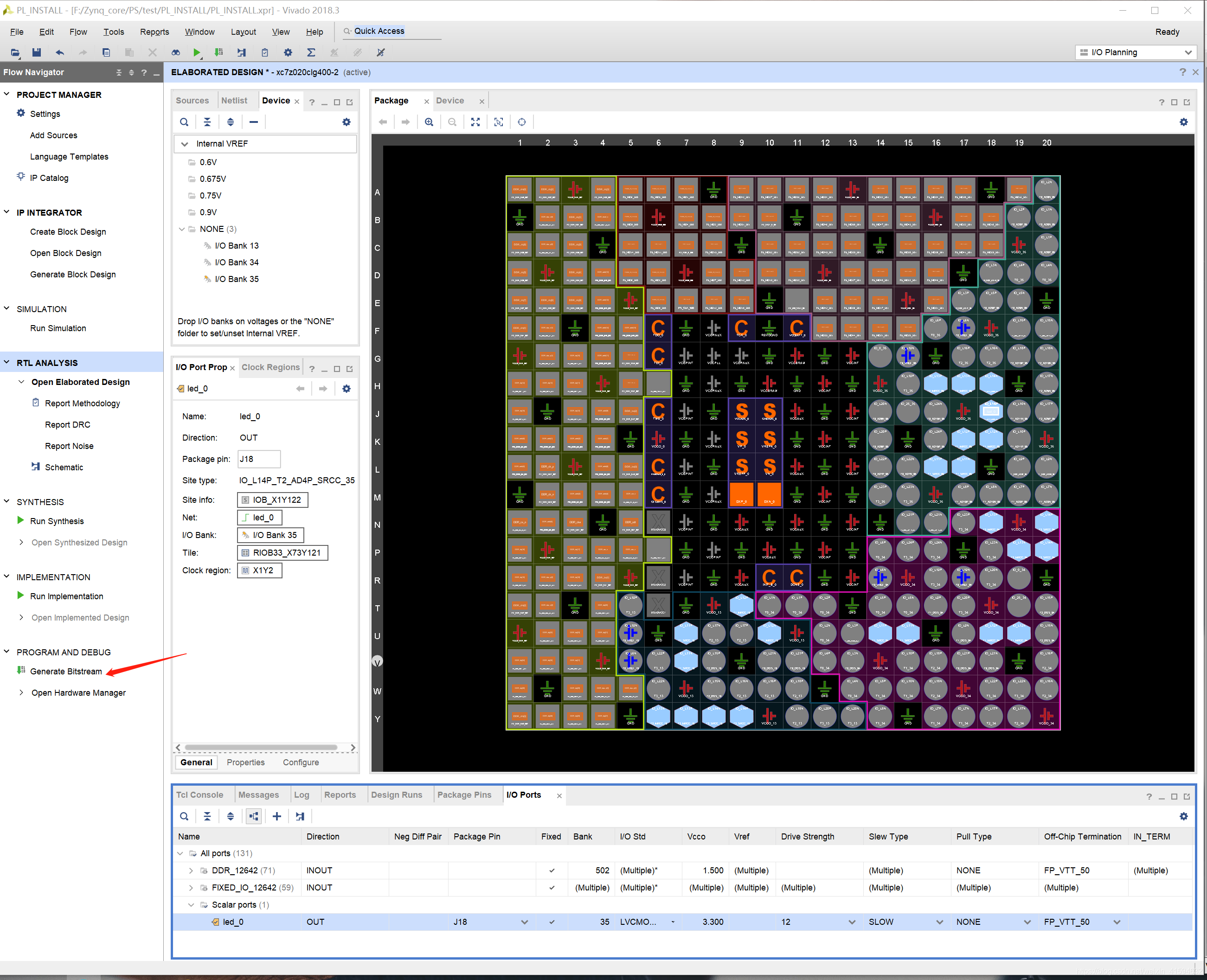

最后生成BIT流文件

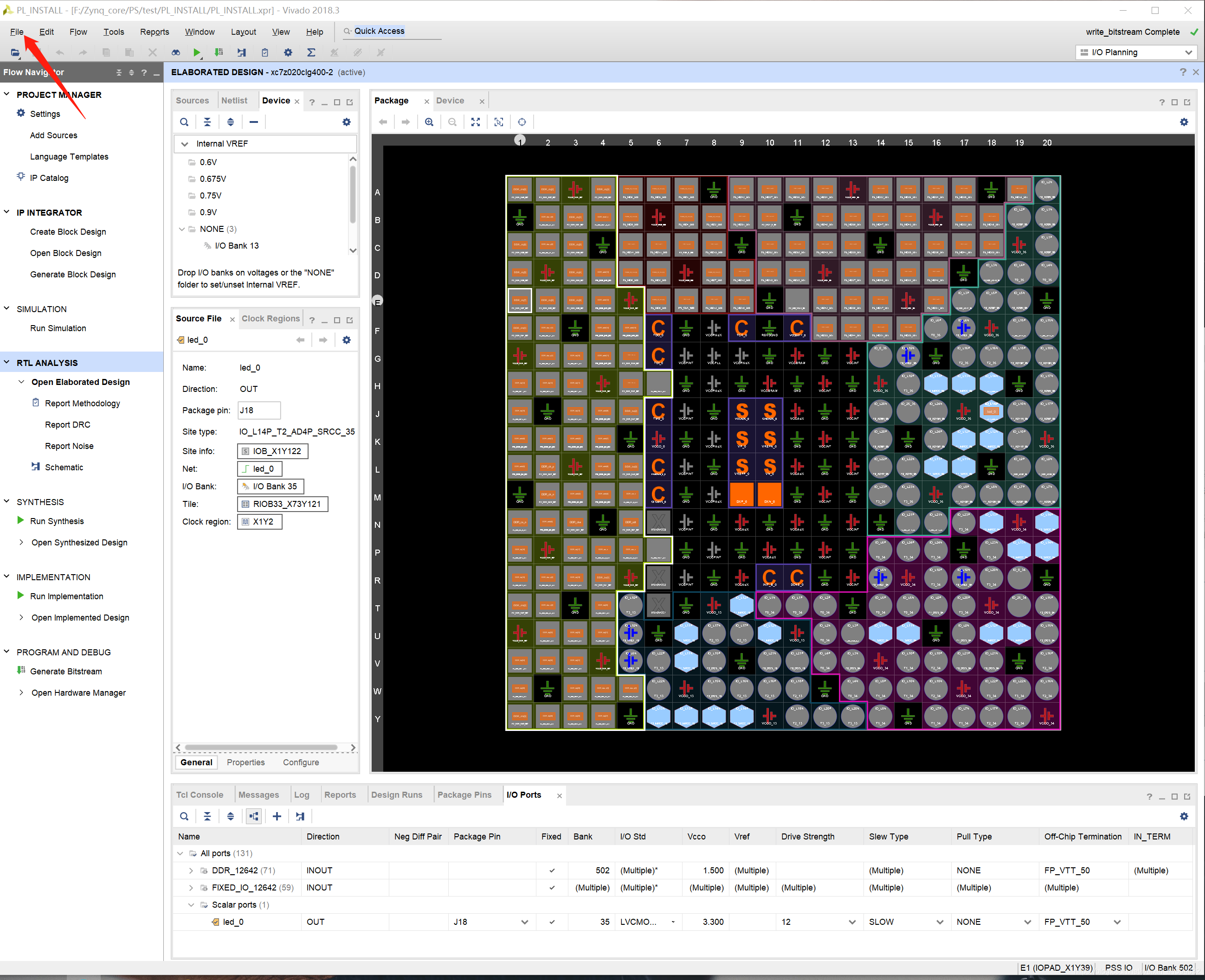

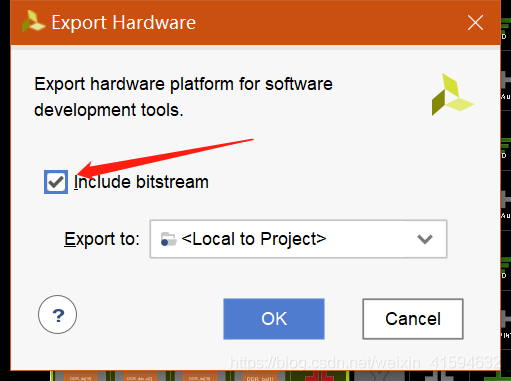

完成后,点击菜单栏中的"file",点击"export"选项中的"export hardware"

注意,一定要在弹出的窗口中选择"include bitstream"选项。

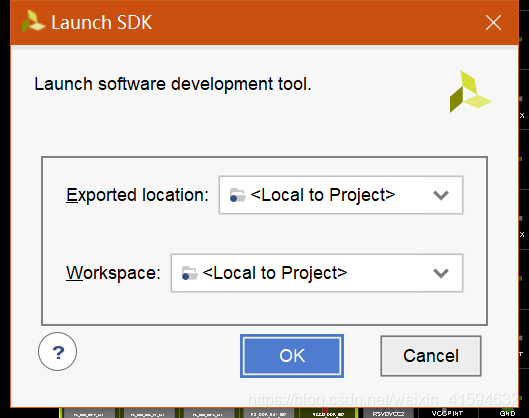

然后点击"file",选择"launch SDK"选项

弹出窗口直接点击OK即可

三 SDK环境下配置

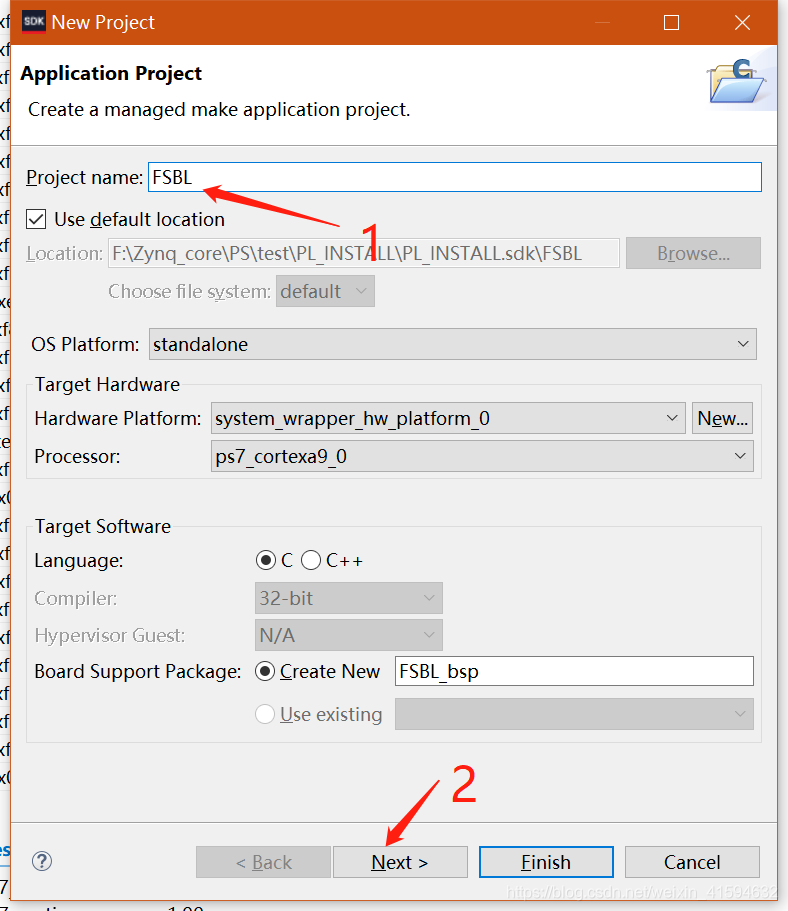

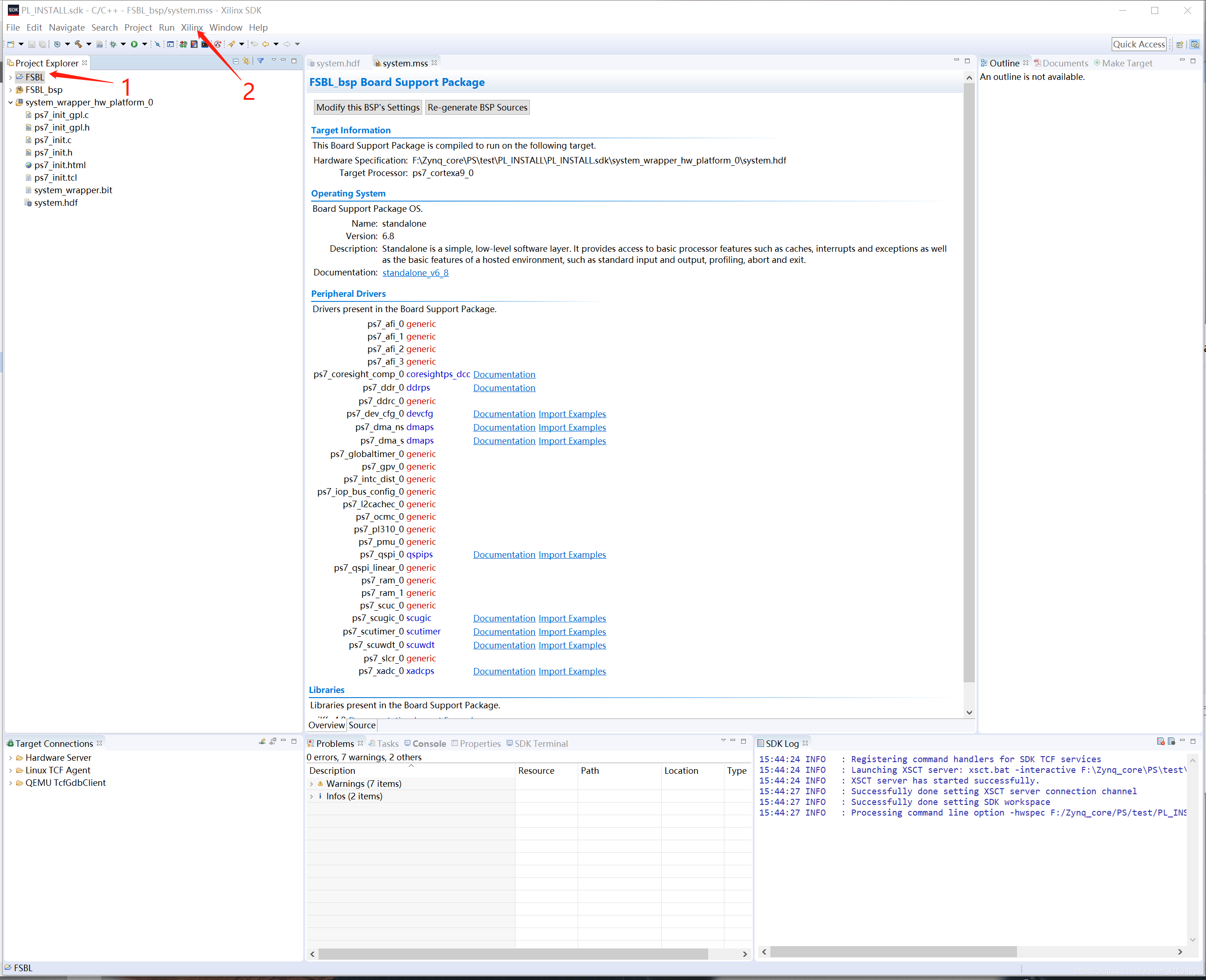

打开SDK后,新建一个应用工程。按下快捷键"alt+shift+n",弹出的窗口选择"application project"。新建一个名为FSBL的工程

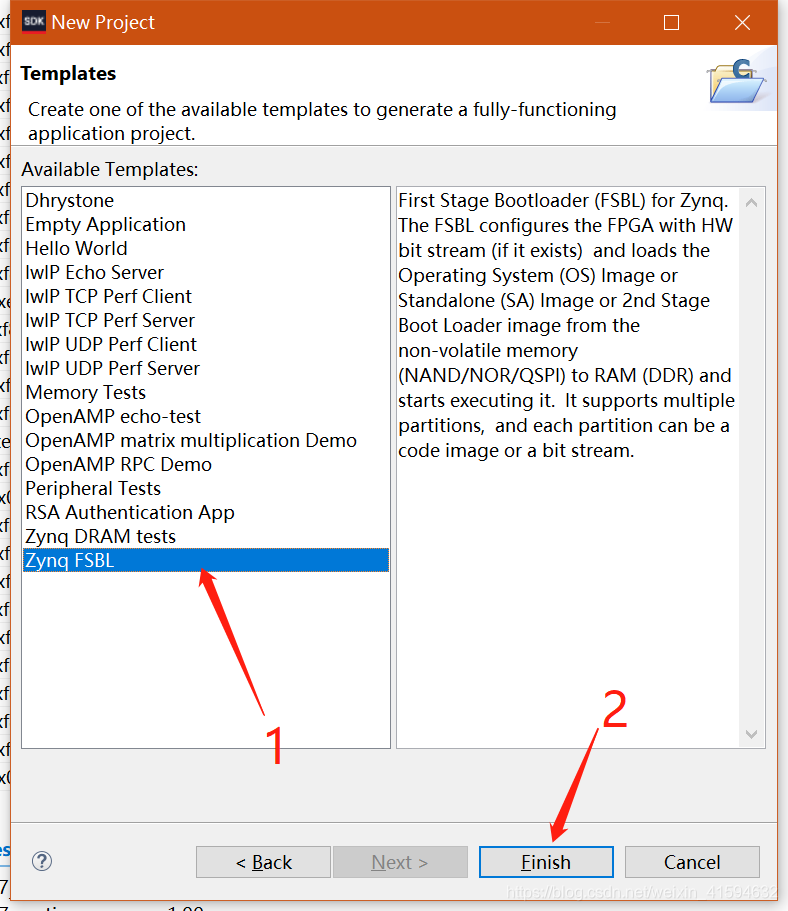

选择新建一个FSBL项目模板

创建完成后,先点击新建的FSBL工程,然后点击菜单栏中的"Xilinx"选项,选择"Create Boot Image"

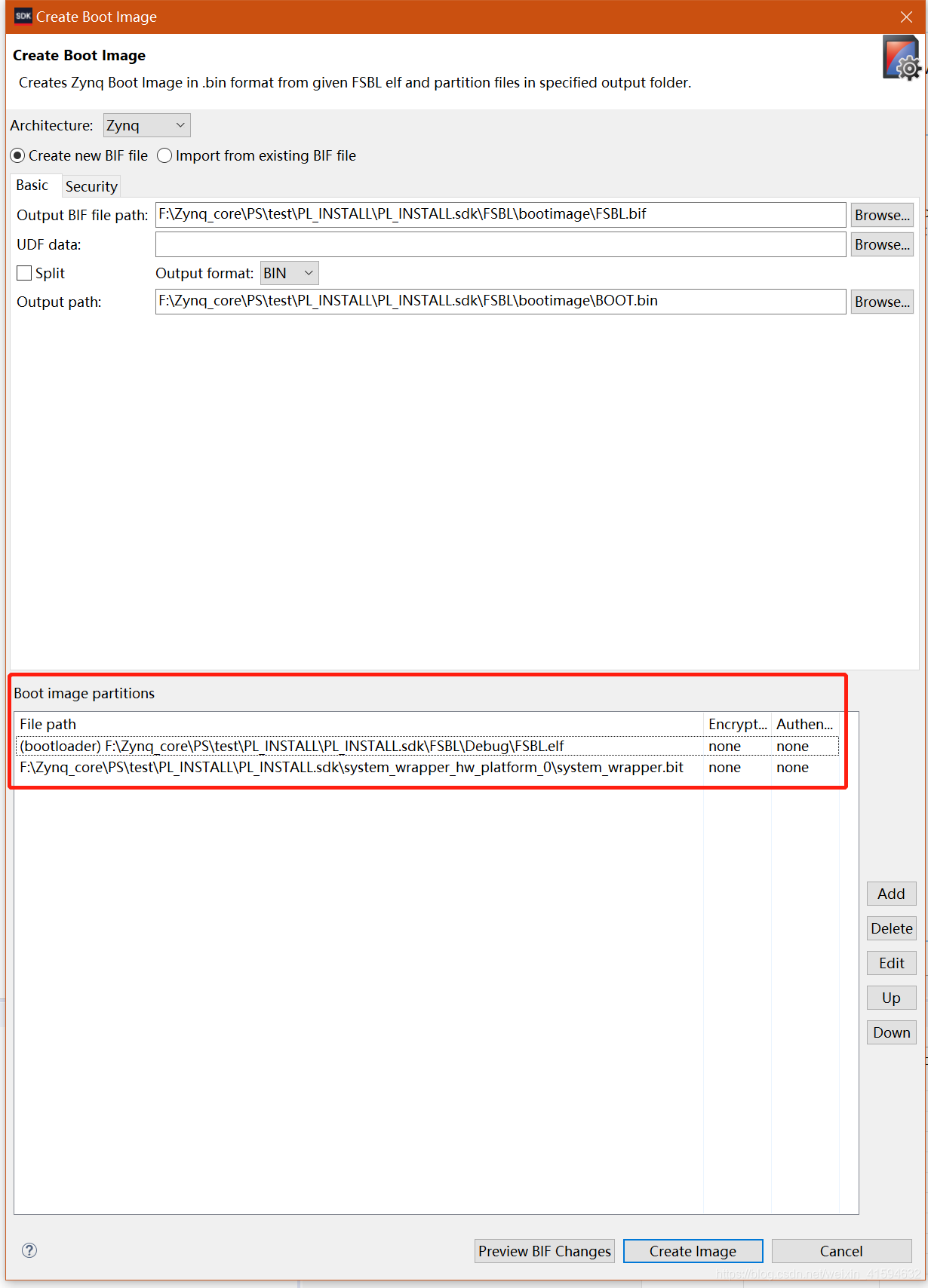

在弹出的窗口中,"Boot Image partitions"中有两个文件,其中"FSBL,elf"是bootloader启动文件,"system_wrapper.bit"是配置PL端资源的bit流文件。确保这两个文件都存在后,点击"Create Image"即可。另外需要注意的是,一定要保证"FSBL.elf"这个文件在"system_wrapper.bit"上面。如果弹出的窗口中没有自动添加进这两个文件,可能是因为没有选中FSBL工程后在点击"Create Boot Image"

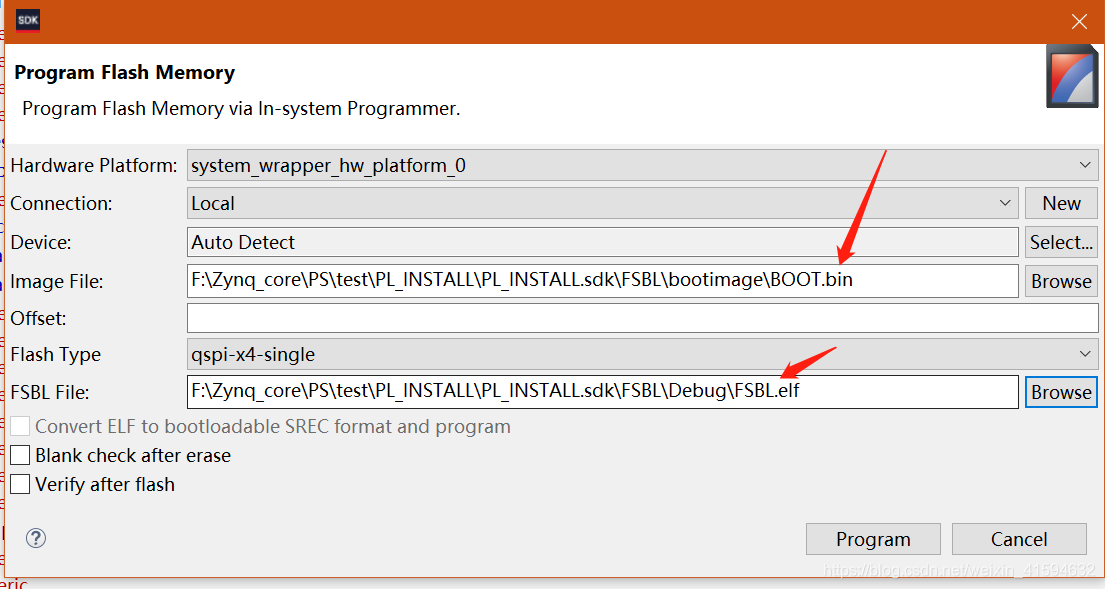

接下来再次点击菜单栏中的"Xilinx"选项,这次选择"Program Flash",在弹出的窗口中添加BOOT.bin和FSBL.elf这两个文件的路径

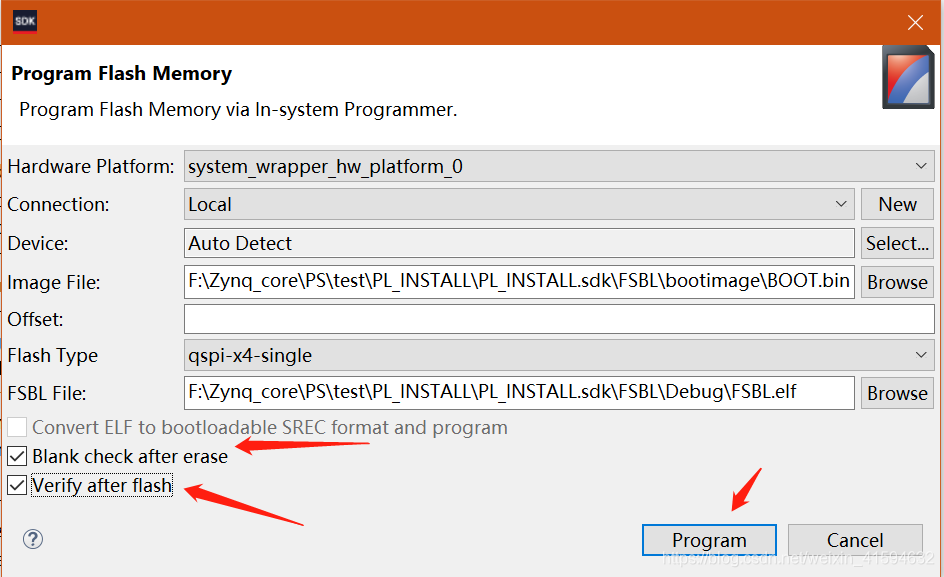

勾选这两个选项,然后点击"program",等待烧录完成就ok啦

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)