Xilinx PCIe axi memory mapped(XPDMA)手册笔记

最近新调试的一个项目,用的PS端芯片只支持memory mapped模式,原来的XDMA的PCIE不能用,连Link都找不到,只能重新学习这个新的IP核的使用。a). 官方手册地址链接:https://china.xilinx.com/support/documentation/ip_documentation/axi_pcie/v2_8/pg055-axi-bridge-pcie.pdfb)..

驱动参考另附:https://www.xilinx.com/support/answers/65444.html

https://github.com/Xilinx/dma_ip_drivers

最近新调试的一个项目,用的PS端芯片只支持memory mapped模式,原来的XDMA的PCIE不能用,连Link都找不到,只能重新学习这个新的IP核的使用。

a). 官方手册地址链接:https://china.xilinx.com/support/documentation/ip_documentation/axi_pcie/v2_8/pg055-axi-bridge-pcie.pdf

b). xapp1171文档链接: https://www.xilinx.com/support/documentation/application_notes/xapp1171-pcie-central-dma-subsystem.pdf (PCI Express Endpoint-DMA Initiator Subsystem)

c). 另外在网上还看到一个链接:https://www.amobbs.com/thread-5693775-1-1.html?_dsign=1015f699 (请教关于AXI Memory Mapped to PCIe中DMA传输的问题,即AXI:BARS作用)文章中有提到使用这个IP核需要添加一个CDMA的IP核,然后通过AXI总线配置好CDMA的目的地址和源地址,可以参考Xilinx的XAPP1171。

d). https://github.com/strezh/XPDMA (XPDMA软件驱动以及FPGA工程脚本链接,PCIe DMA Subsystem based on Xilinx XAPP1171)

e).另外网上有人编写了PCIE memory mapped 的IP核设置的Vivado操作文档

链接:https://pan.baidu.com/s/1tZ3-ZynE6hX_MTgV2I2sVA 提取码:sl8y

-

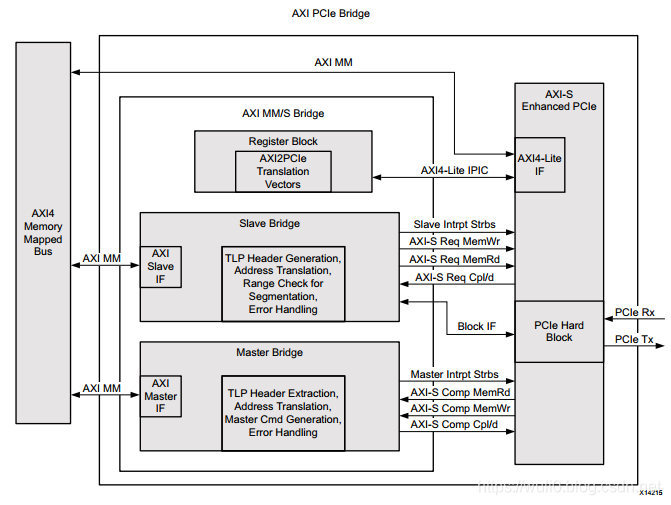

AXI PCIE桥内核模块框图

-

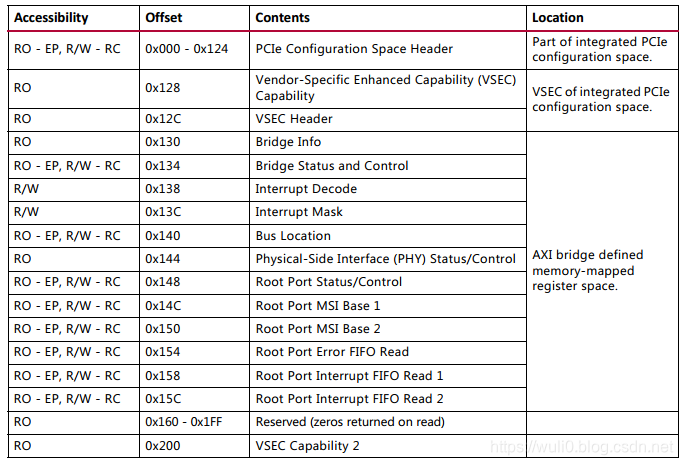

对于Register Block映射的寄存器地址如下:

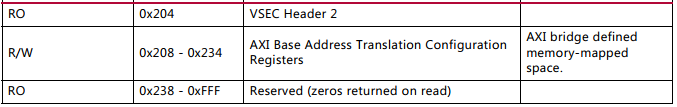

我们重点关注的寄存器是AXI Base Address Translation Configuration Registers (Offset0x208 - 0x234)

只有当C_INCLUDE_BAR_OFFSET_REG = 1时, 才包括这些寄存器。

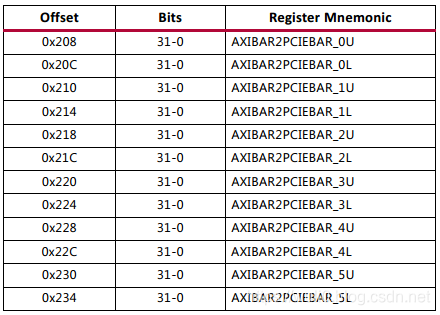

下面这些寄存器

208表示AXI_BAR转到PCIE_BAR0高32bit的地址

20c表示AXI_BAR转到PCIE_BAR0低32bit的地址

210表示AXI_BAR转到PCIE_BAR1高32bit的地址

214表示AXI_BAR转到PCIE_BAR1低32bit的地址

。。。。。。

这个怎么理解呢,比如说:

addr:0x208=0x0000_0000,addr:0x20c=0xfe00_0000;

在外部总线交互模块中,BAR0的基地址为0x8080_0000;

那么AXI总线往地址0x8080_0000中写入数据,等同于往BAR0的0x0000_0000地址写入数据,映射到PCIE内部后等同于往地址0xfe00_0000中写入数据。

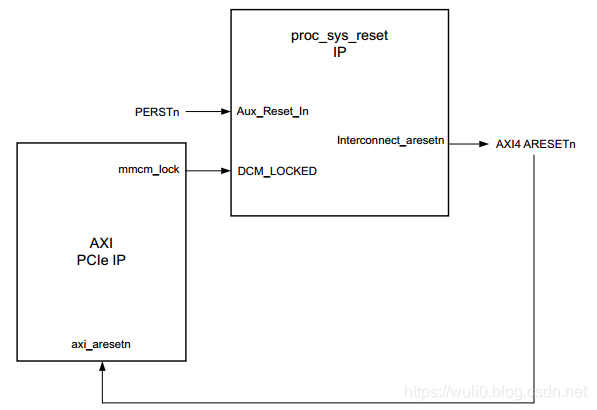

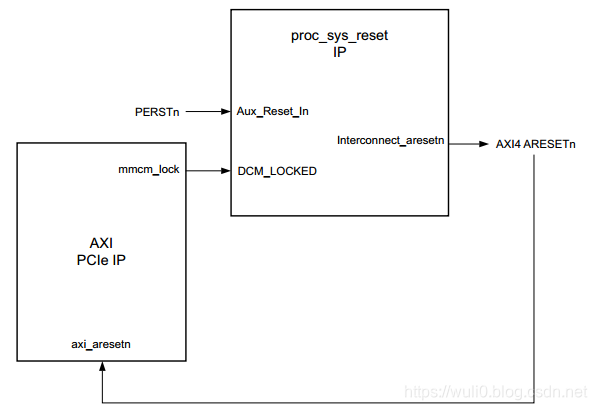

- 时钟与复位

时钟需要注意的是PCIe Reference Clock一般为100Mhz,axi_aclk_out只有x1 gen1 64-bit AXI为62.5Mhz,其余都是125Mhz。

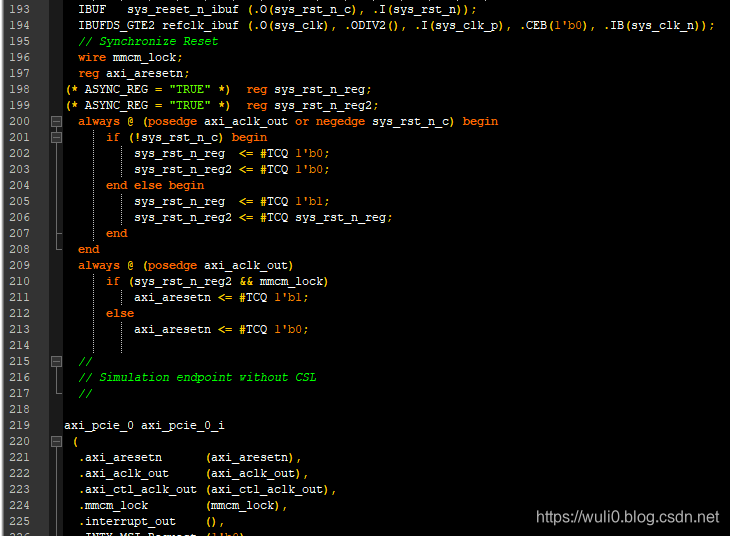

复位需要注意的是axi_aresetn不能直接连外部的复位信号,需要使用mmcm_lock信号过proc_sys_reset做同步处理

一般来讲我们建议也可以产用下面的方法对PCIE的复位信号做异步复位同步释放处理,以下代码来自IP核的example工程。大家可以自己去研究。

如果axi_aresetn直接接到PCIE外部的管教会出现Link不上的情况

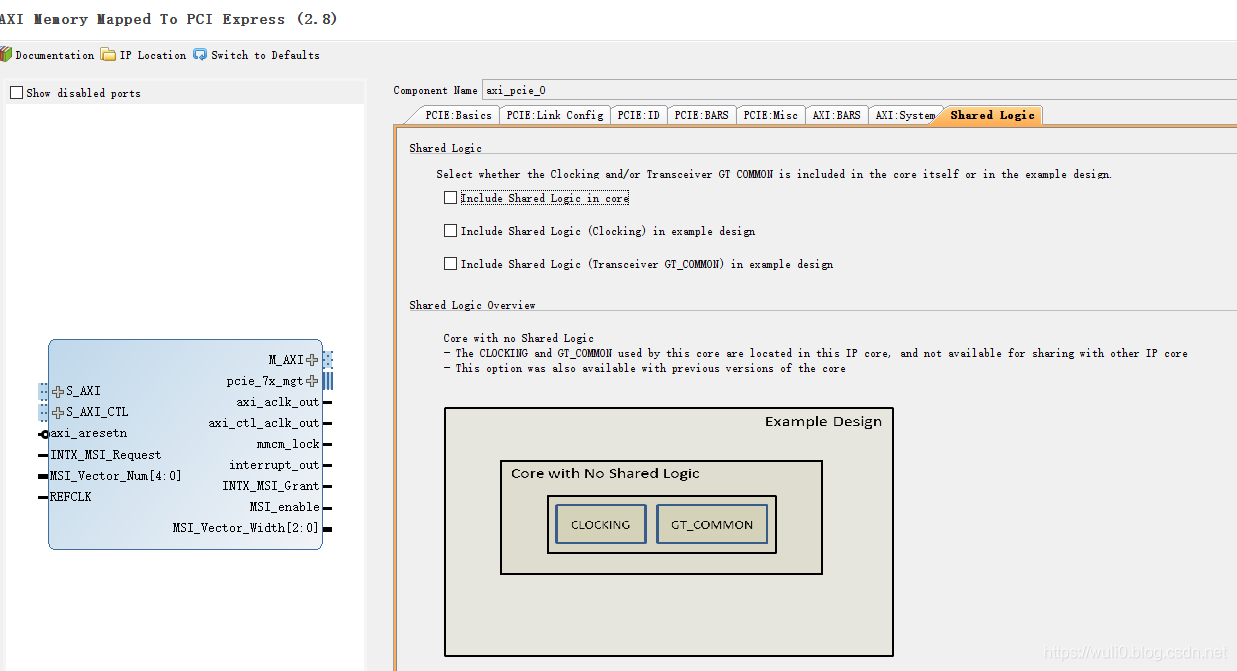

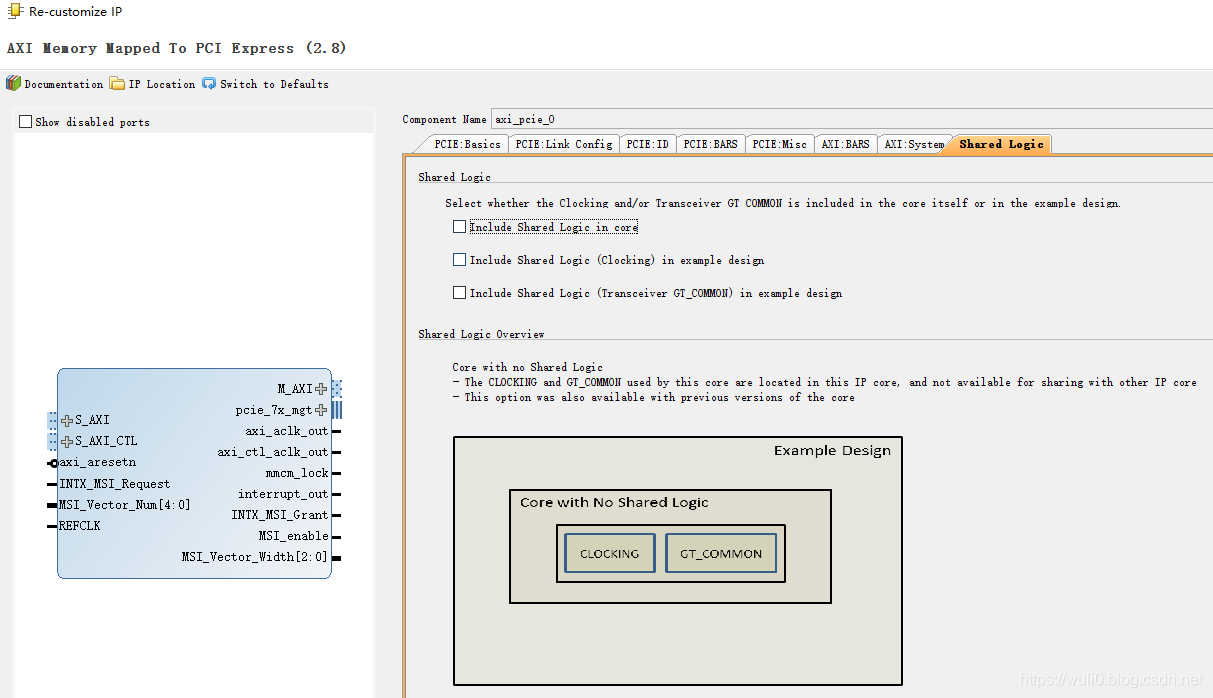

- 关于共享逻辑

这个功能允许在多个实例化中共享公共块。它可以最大限度地减少所需的 HDL 修改。可以使用自己的系统级时钟或复位电路。可以根据系

统要求修改其中的一些块 (例如, 将 BUFG 换成 BUFH)。可以实例化多个内核并共享所有实例化内核中的一个核心的 “公共共享逻辑”。既适用于终结点模式, 也适用于根端口模式。具体不多说,稍微看看就会用。

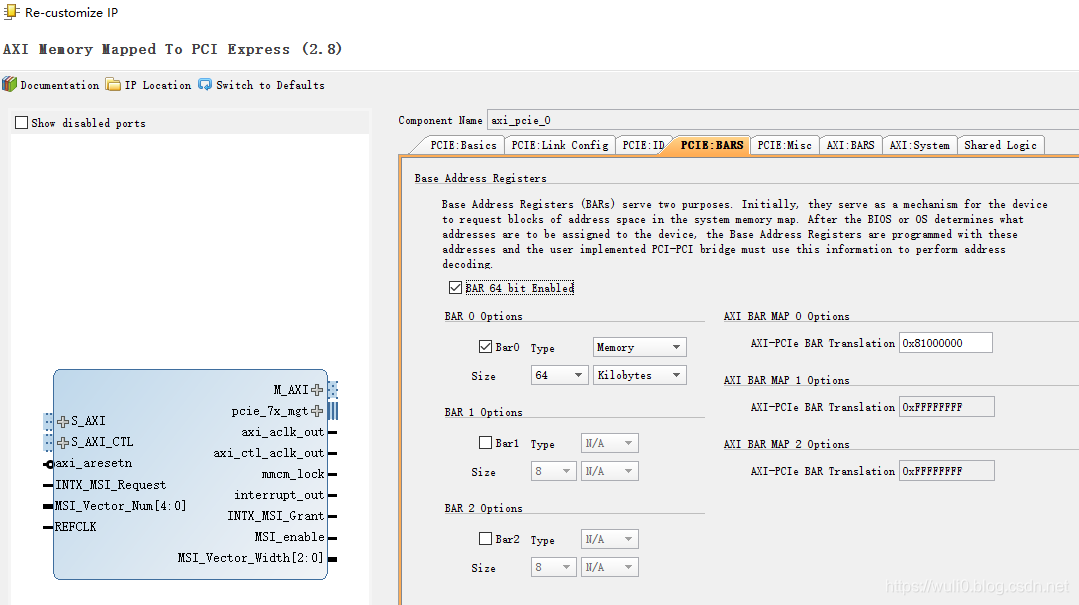

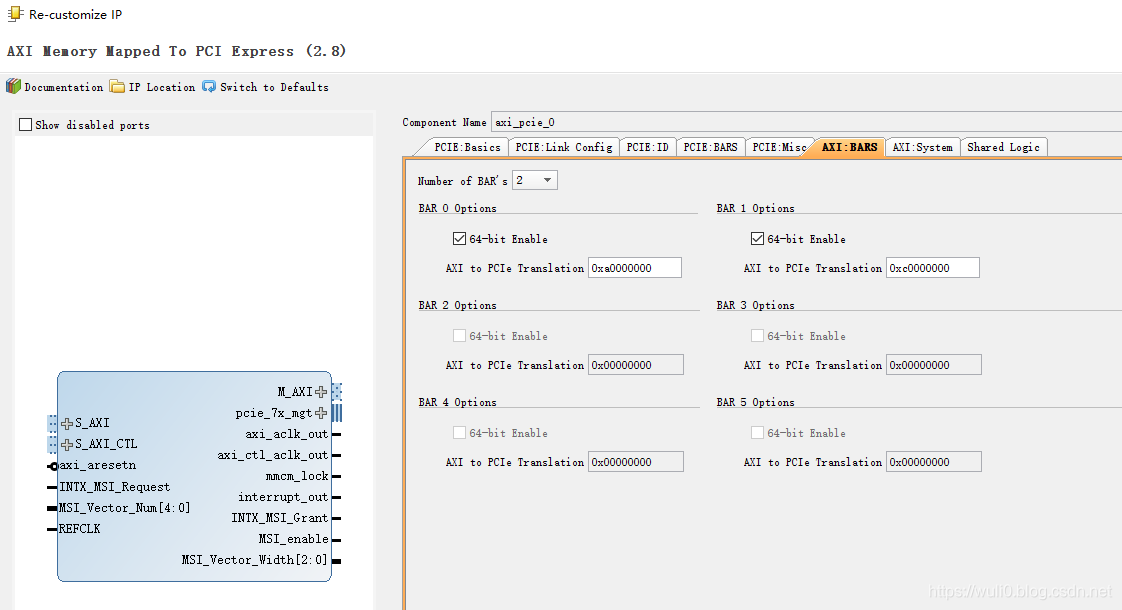

- BAR地址映射的主要参数为:

PCIe端支持的桥接最多可映射三个64位BAR用于PCIe:C_PCIEBAR_NUM, C_PCIEBAR2AXIBAR_n和C_PCIEBAR_LEN_n

其中n表示PCIe的特定BAR编号,从0到2。

在AXI端,桥接器支持最多六个32位或64位AXI基地址寄存器(BAR)映射到PCIe:

C_AXIBAR_NUM, C_AXIBAR_n, C_AXIBAR_HIGHADDR_n, C_AXIBAR2PCIEBAR_n和C_AXIBAR_AS_n

其中n表示从0到5的AXIBAR编号。

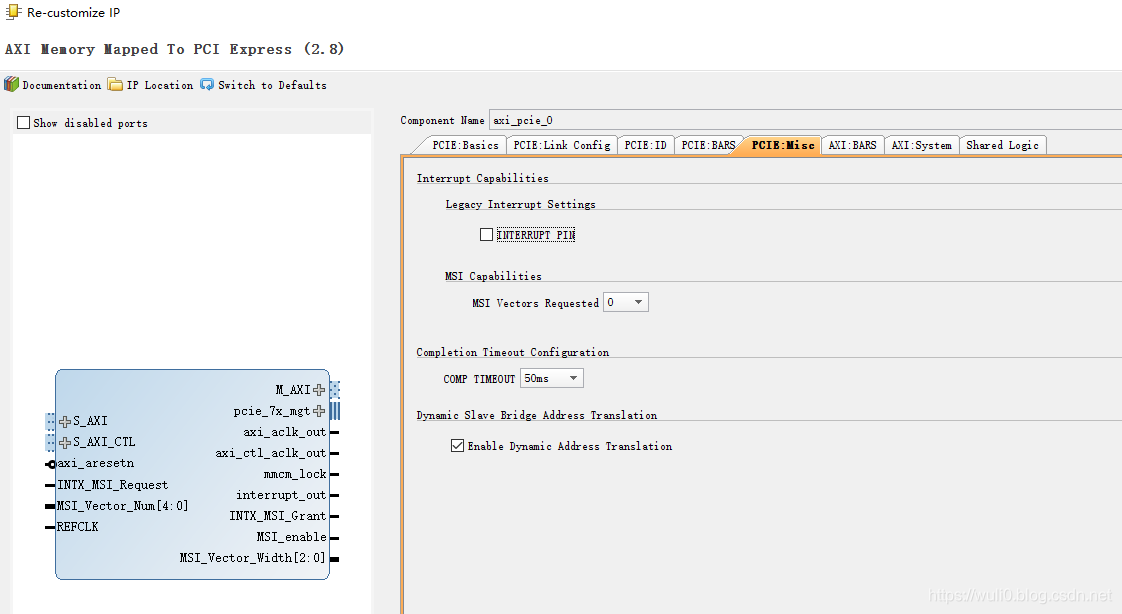

需要注意的是:C_INCLUDE_BAROFFSET_REG允许动态地址转换,当此参数设置为1时,可以更改AXIBAR2PCIEBAR_n转换向量

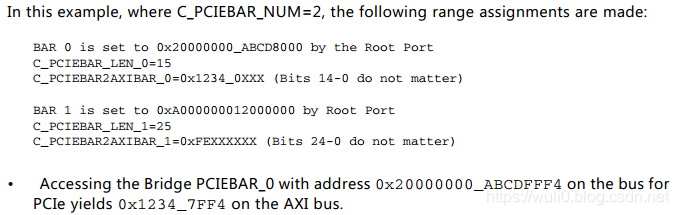

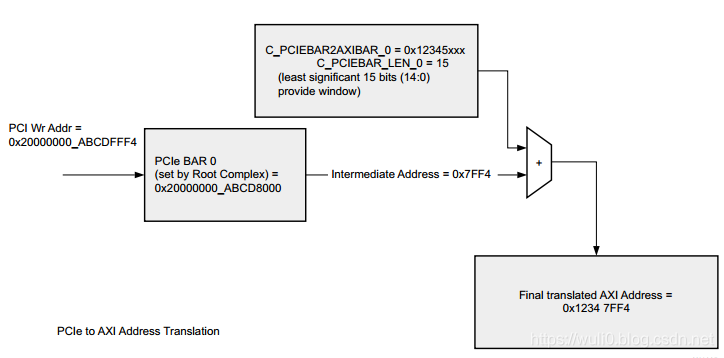

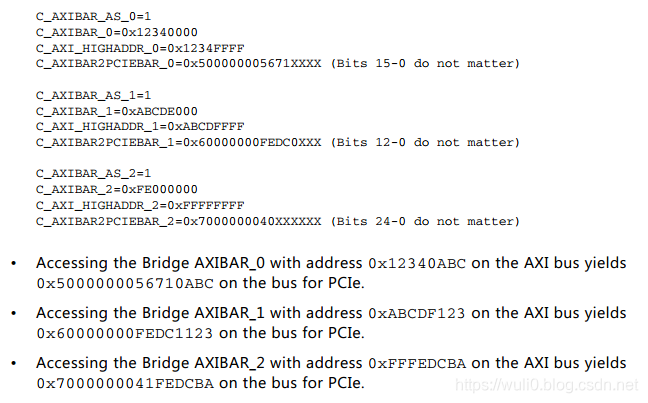

下面是手册上的例子,还是比较好理解的:

1)PCIEBAR2AXI:

2)AXI2PCIEBAR:

- 中断

interrupt_out引脚可根据中断屏蔽寄存器的设置为发送中断。 interrupt_out引脚向连接到桥接器的存储器映射AXI4侧的设备发出中断信号。中断屏蔽和中断解码寄存器中定义的MSI中断用于指示接收到消息信号,仅当桥以根端口模式运行时(C_INCLUDE_RC = 1)才中断。

MSI Interrupt中断,仅当桥以端点模式(C_INCLUDE_RC = 0)运行时,intx_msi_request引脚输入才有效

Legacy Interrupts中断,当桥以端点模式(C_INCLUDE_RC = 0)运行时,intx_msi_request引脚输入才有效。

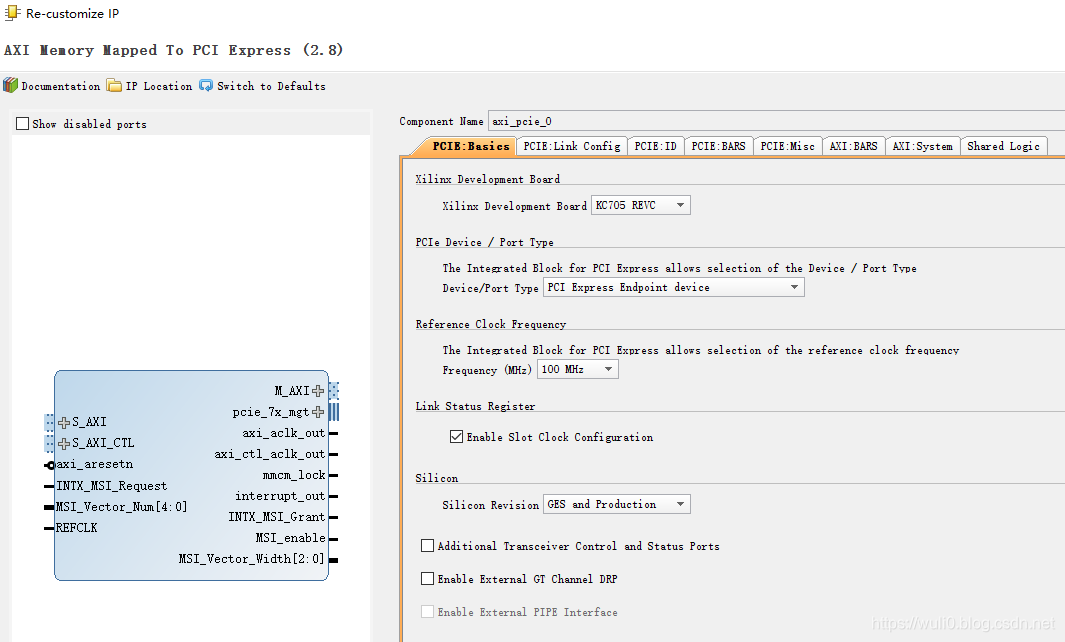

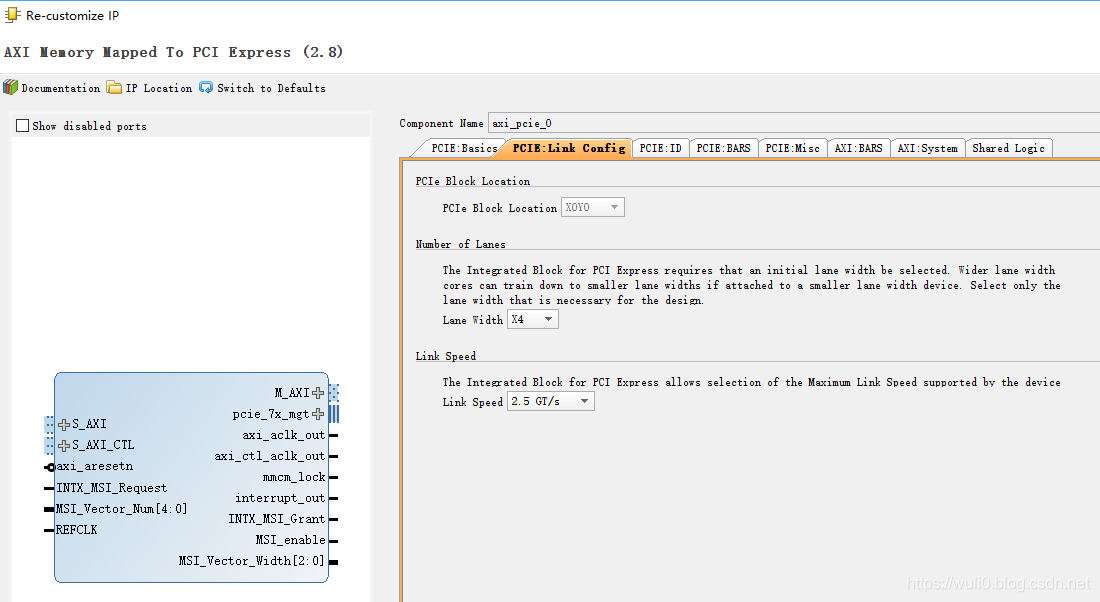

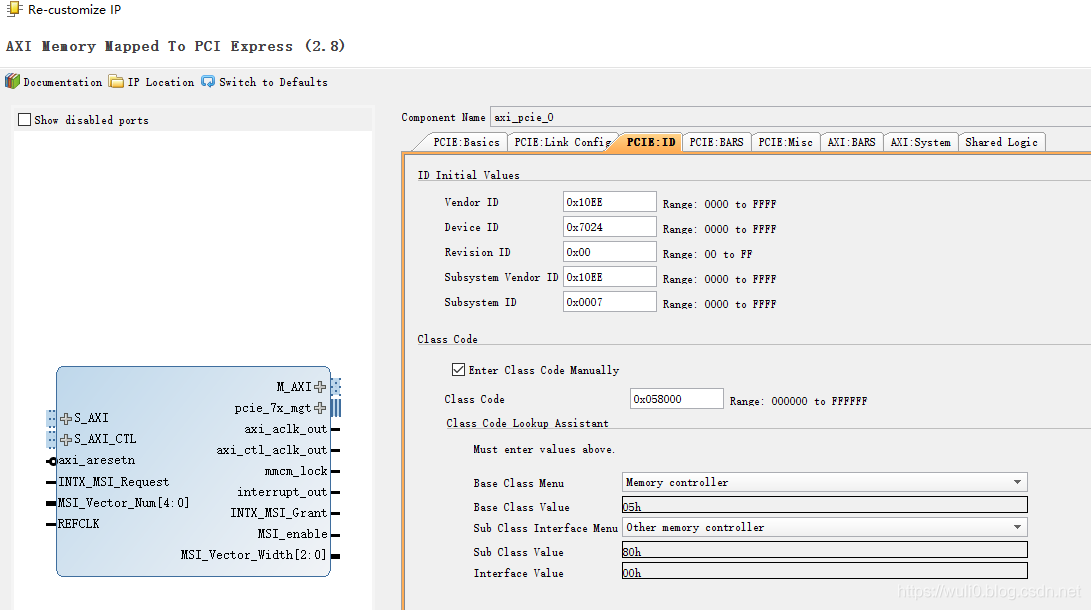

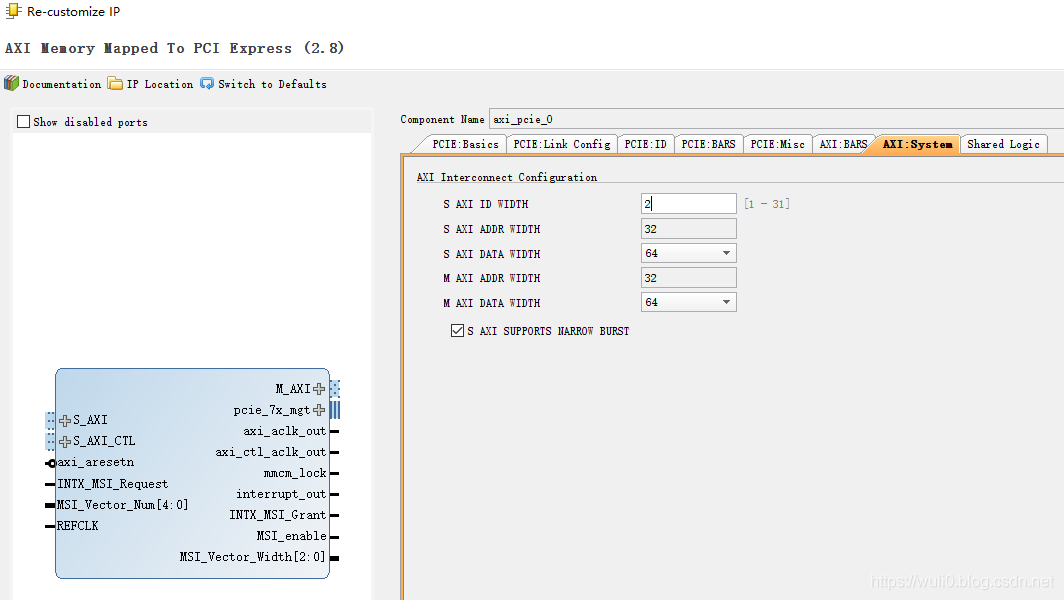

7.内核定制

有关更加详细的信息请参考IP核文档。。。。。。

目前这个 IP核正在调试,后续调好后还会继续补充。。。。

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)