SerDes系列之FFE均衡技术

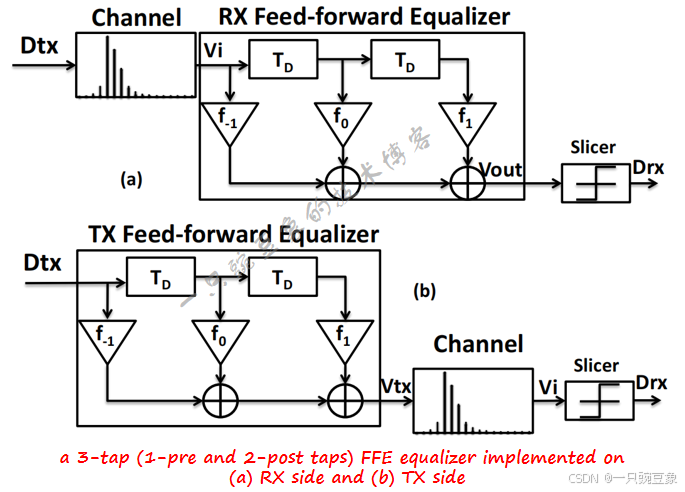

FFE的基本结构可以在RX侧或TX侧实现,其基本工作原理相同:它通过从同一信号源应用适当的延迟来产生多径信号,然后对它们进行线性缩放和组合以消除信道ISI。

Feed-forward Equalizer (FFE)

FFE的基本结构可以在RX侧或TX侧实现,其基本工作原理相同:它通过从同一信号源应用适当的延迟来产生多径信号,然后对它们进行线性缩放和组合以消除信道ISI。

以一个简单2抽头、1单位(1-UI)间隔的前馈均衡器(FFE)为例,来进一步研究其线性特性:

其中f0是主抽头(当前比特位)、f1是校正抽头(前一个比特位),并假设两者都是正的。f1之前的负号是为了实现FFE的高通滤波功能,这样它就可以“均衡”通道的低通特性。

当前一个比特和当前比特不同(例如,Vin[k] = -Vin[k - 1],即时钟模式的情况)时,就会发生电平瞬态变化,此时数据中包含一个高频分量,该高频分量在经过低通信道时会遭受更大的损失,因此,将从前馈均衡器(FFE)获得(f0 + f1)的最大增益;

另一种情况,在连续比特(例如,Vin[k] = Vin[k - 1],这是一种直流(DC)模式的情况)的传输/接收过程中,FFE将为低频数据流产生(f0 - f1)的最小增益。

正是基于上述的(f0 + f1)/(f0 - f1)增益提升机制,FFE可以通过增加信道的高频成分来扩展整个信道带宽以匹配整体低频增益。

然而,由于均衡器引入的高频增益必须大于其低频增益才能扩展带宽,因此FFE会放大更多的高频噪声(例如串扰噪声),从而往往会损害链路的整体均衡信噪比(SNR),并且,需要均衡的ISI越多(即更大的增益提升),高频噪声就会被放大越多。

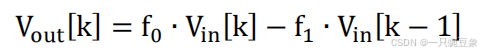

发射机整体结构如下图所示,由于复杂的分段逻辑,大量的TX预加重抽头极易导致预驱动器功率过大,因此在本文中,仅讨论实现2个预加重抽头。

Pre-emphasis Decoder

发射机(TX)有限脉冲响应(FIR)滤波器本质上是高通滤波器,预加重解码器只需查找当前比特与下一个或前一个比特之间的差异或相似之处(使用异或运算和与运算),以便为拉高(pull-up)、拉低(pull-down)和分流(shunt)器件提供适当的信号。

进行这种预解码(Pre-emphasis Decoder)的主要目的是,这些逻辑门可以在所有最终驱动段之间共享,然后,每个单独的驱动段只需要包含多路复用器(MUXes),以决定是使用预解码器的输出还是直接使用原始数据位。 与每个驱动段内都需要多个复杂逻辑门的设计相比,该设计将一些逻辑门从驱动段中移出,放入了一个共享的预驱动逻辑中,从而显著降低了数字功耗开销。

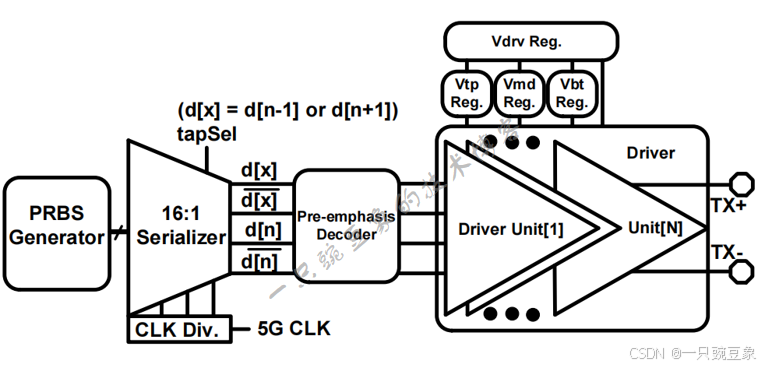

Driver Segments

驱动段指的是全摆幅逻辑数据与传输的低摆幅模拟信号之间的接口。由于该设计的特点是低电压摆幅(差分振幅≤250mV),因此,每个驱动段都采用了N对N-MOS电压模式驱动器。同样,由于输出共模电压低,分流器件也采用NMOS晶体管实现。

N对N支路的供电电压连接到由摆幅控制调节器生成的Vdrv。上拉、下拉和分流器件的栅极电压分别连接到3个缓冲器,这些缓冲器的供电电压分别为Vtp、Vbt和Vmd,它们由阻抗控制调节器生成。

上拉、下拉和分流器件的尺寸被设定为提供大致相等的Vtp、Vbt和Vmd,以便使这三个路径上的缓冲延迟能够大致匹配。缓冲链由偶数个反相器组成,以平衡不同工艺角(Corner)的上升和下降时间。

如果驱动段被启用为预加重模式,则该段内的多路复用器(MUX)会将上拉、下拉和分流器件的栅极连接到预解码器的输出,该预解码器会对当前位与下一位或上一位进行比较。

如果驱动段未配置为预加重模式,则分流器件将接地,而上拉和下拉器件将仅由当前位驱动。采用这种仅由2输入多路复用器和电平移位反相器组成的简化段逻辑,可以将每个高速数字门驱动器功耗降至较低的水平。

Measurement Result

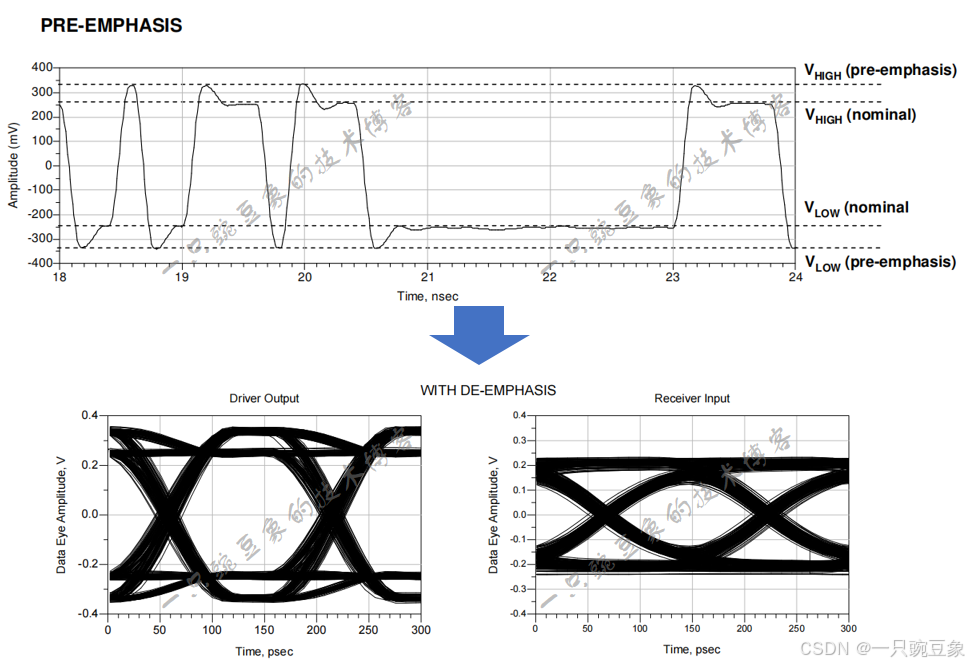

从波形上直观地观察,预加重就是是将任何相等位值序列中的第一个bit位设置到比其余bit位更高的电压水平,以补偿因高频衰减损失的高频分量,从而保证最终的眼图电压摆幅的最大化和稳定性。

本文仅讨论了FFE技术中的预加重功能,与其相对应的,还有去加重功能,二者原理是相通的。

参考文献

[1] Energy-Efficient Equalization Circuits for High-Speed Wireline Links.

更多推荐

已为社区贡献18条内容

已为社区贡献18条内容

所有评论(0)